A kind of programming test method of phase change memory

A phase change memory and phase change storage technology, which is applied in the field of programming and testing of phase change memory, and can solve problems such as data operation failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

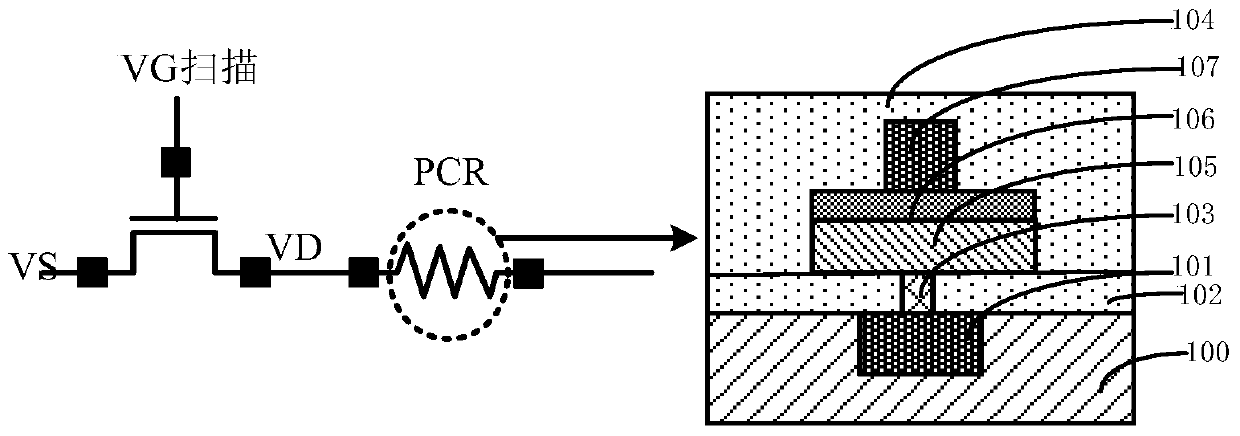

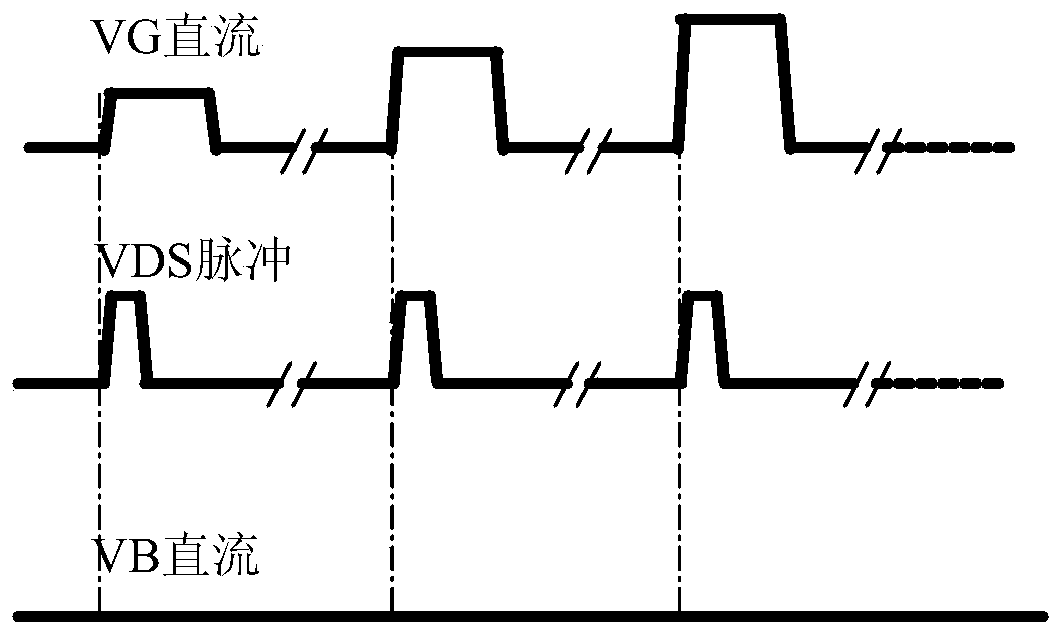

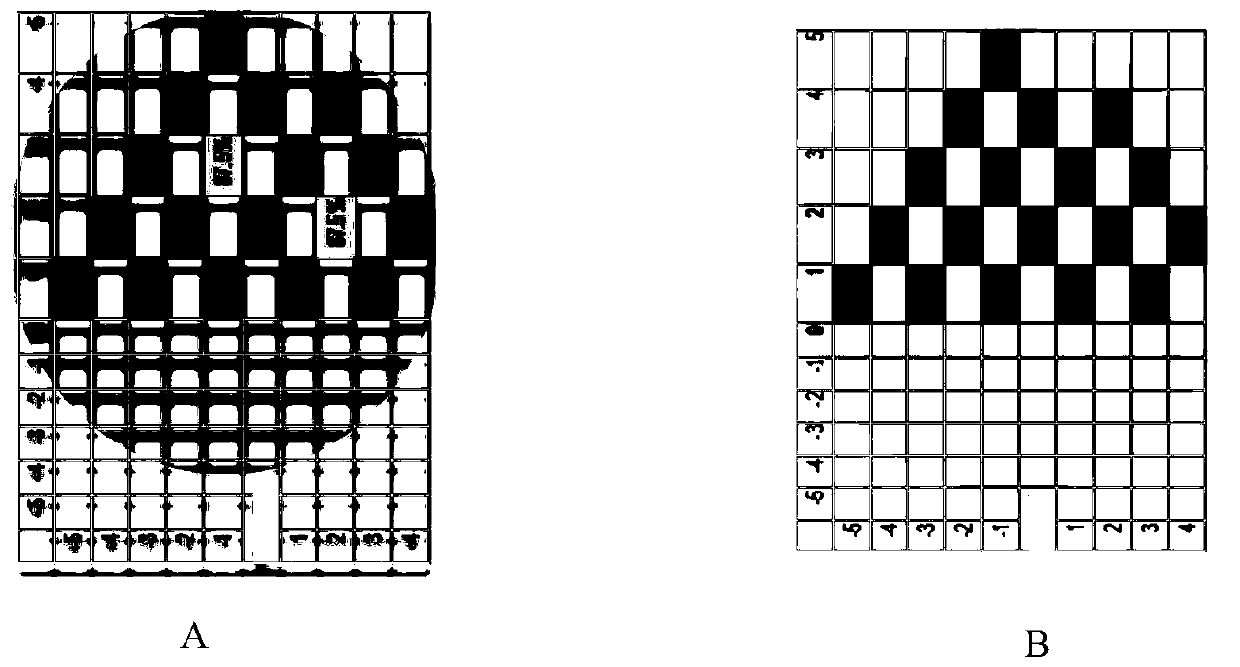

[0037] In order to solve the problems in the prior art, the present invention provides a programming and testing method of phase change memory, and the method of the present invention will be further described below in conjunction with the accompanying drawings. in, figure 1 It is a structural schematic diagram of the programming and testing method of the phase change memory described in a specific embodiment of the present invention; figure 2 It is a schematic diagram of the voltage in the programming and testing method of the phase change memory described in a specific embodiment of the present invention; image 3 It is the yield distribution diagram of the programming test method of phase change memory, wherein A is the yield distribution diagram of the programming test method of phase change memory in the present invention, and B is the yield distribution of the programming test method of phase change memory in the prior art picture.

[0038] The invention discloses a p...

Embodiment 2

[0066] In order to solve the problems in the prior art, the present invention provides a method for programming and testing phase change memory. The method of the present invention will be further described below in conjunction with the accompanying drawings. in, figure 1 It is a structural schematic diagram of the programming and testing method of the phase change memory described in a specific embodiment of the present invention; figure 2 It is a schematic diagram of the voltage in the programming and testing method of the phase change memory described in a specific embodiment of the present invention; image 3 It is the yield distribution diagram of the programming test method of phase change memory, wherein A is the yield distribution diagram of the programming test method of phase change memory in the present invention, and B is the yield distribution of the programming test method of phase change memory in the prior art picture.

[0067] The invention discloses a meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com