A multi-objective noc test planning optimization method

A technology of test planning and optimization method, which is applied in the direction of electronic circuit testing, measuring electronics, measuring devices, etc., can solve the problem of destroying chip reliability, etc., and achieve the effects of improving test efficiency, saving test resources, and reducing congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

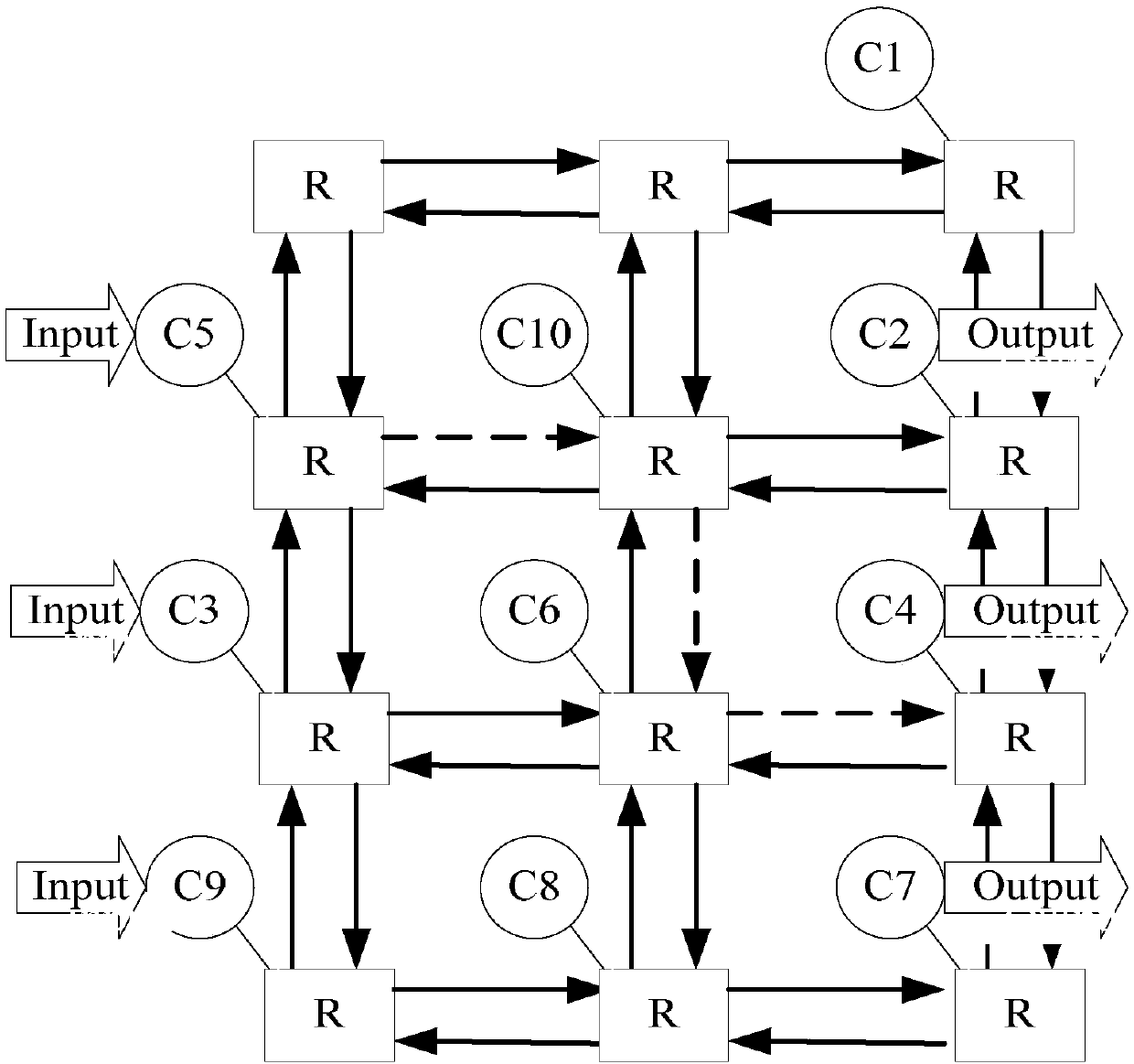

[0040] The NoC involved in the present invention is mainly composed of a router, a network adapter (Network Interface) and a data transmission line (Link) connecting adjacent routers. It is described by topology, routing algorithm, switching mechanism, etc. figure 1 The test example of the d965 system in the 2D Mesh structure in the ITC'02SoC test benchmarks is given, and the routing algorithm adopts the XY routing algorithm. figure 1 There are 3 test ports, and each port is connected to the test pin of ATE (Automatic Test Equipment). Thus, in figure 1 , there are three sets of I / O port pairs that generate test vectors and receive test responses. When testing an IP core, a port pair must be assigned to the IP core. For example: (C5,C4) is a group of I / O port pairs, if C10 (core 10) is assigned to (C5,C4) I / O port pair, the test vector needs to be input from ATE to C5 (core 5), then Then route to C10 (core 10). The test response of C10 (core 10) is output to ATE through C4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com