Transistor and formation method thereof

A technology of transistors and regions, applied in the direction of transistors, electric solid-state devices, semiconductor devices, etc., can solve problems such as unstable performance of SRAM, achieve performance improvement, weaken mismatch problems, and adjust accurately and stably

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

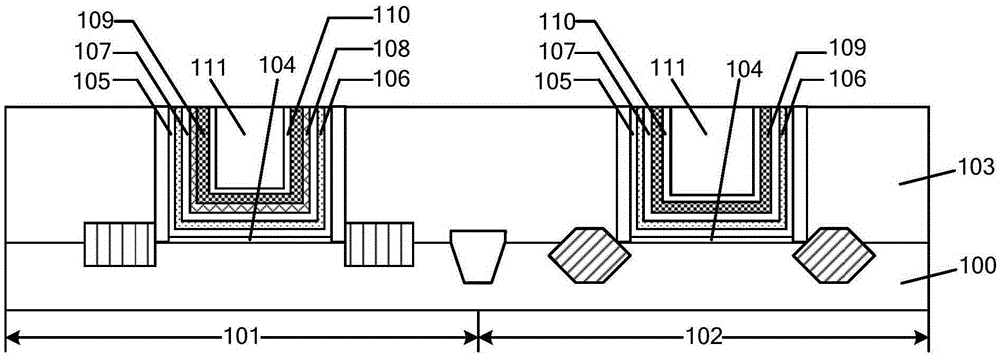

[0036]As mentioned in the background art, due to the difference in work function layer materials required by PMOS transistors and NMOS transistors, the performance of the formed SRAM is unstable.

[0037] After research, it is found that because the storage unit of the SRAM includes a PMOS transistor and an NMOS transistor, and the material of the work function layer required by the PMOS transistor and the NMOS transistor is different. In a PMOS transistor, a P-type work function material, such as TiN, is required between the gate layer and the gate dielectric layer; in an NMOS transistor, an N-type work function material, such as TiAl, is required between the gate layer and the gate dielectric layer. Since the N-type work function material usually has aluminum ions, and the particle size of the aluminum ions is small, the aluminum ions are easy to diffuse into the gate dielectric layer or even the substrate, resulting in changes in the performance of the transistor. Especiall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com