Method of forming a transistor

A technology of transistors and semiconductors, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as poor performance of P-type fin field effect transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

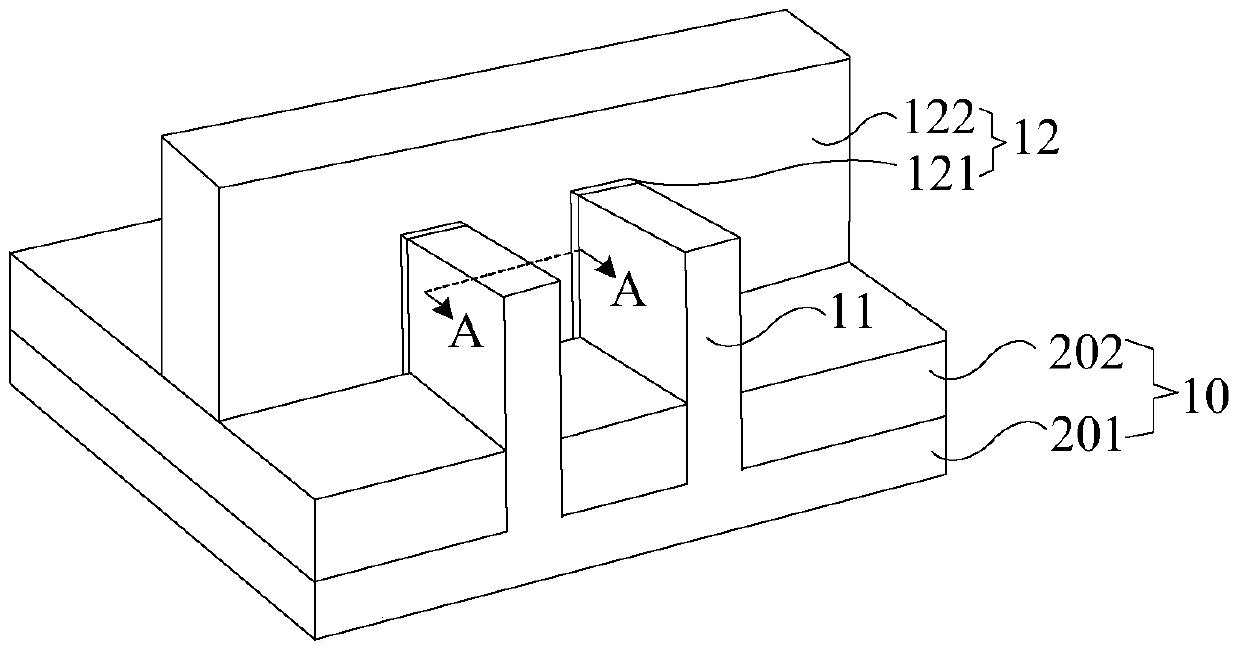

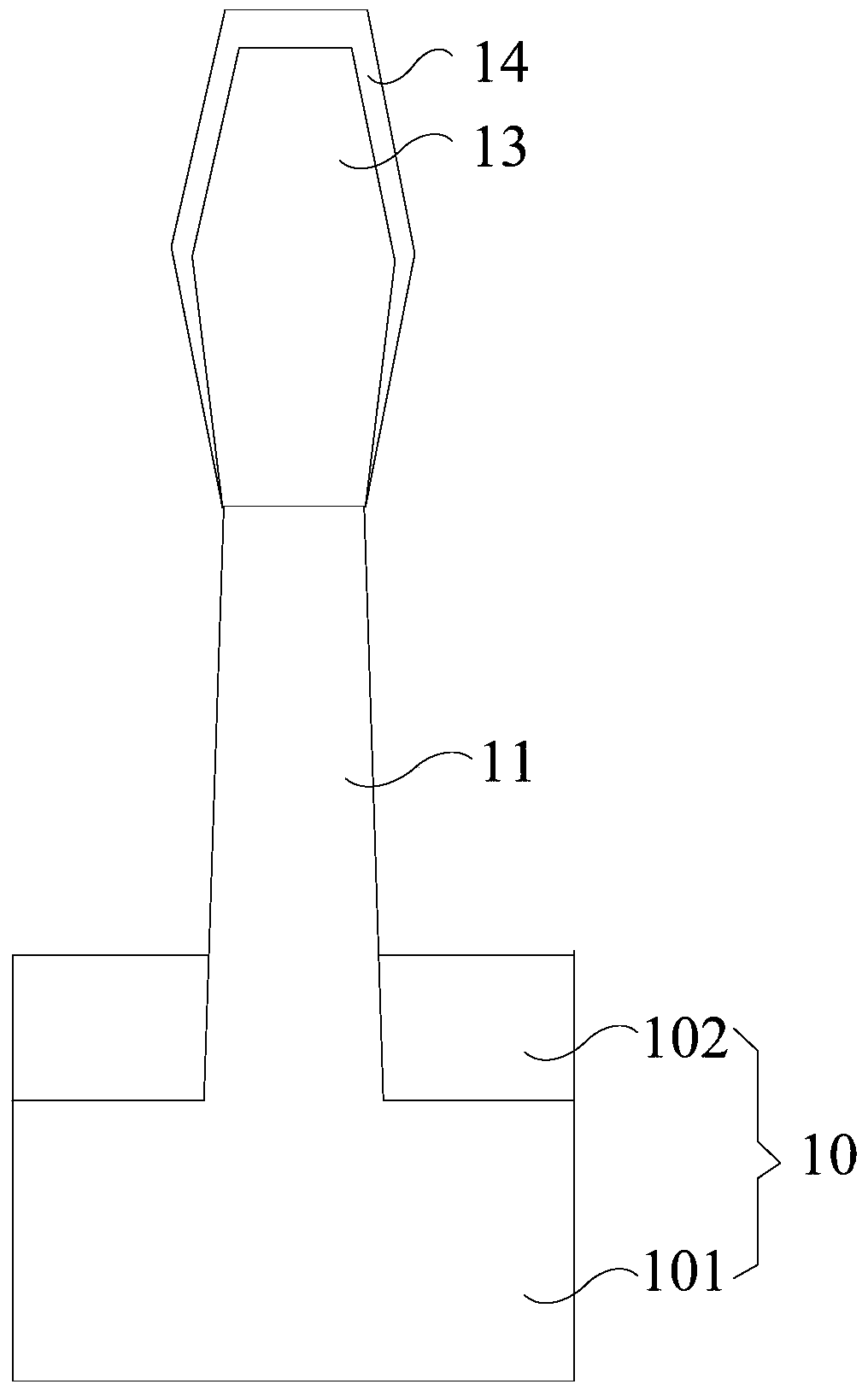

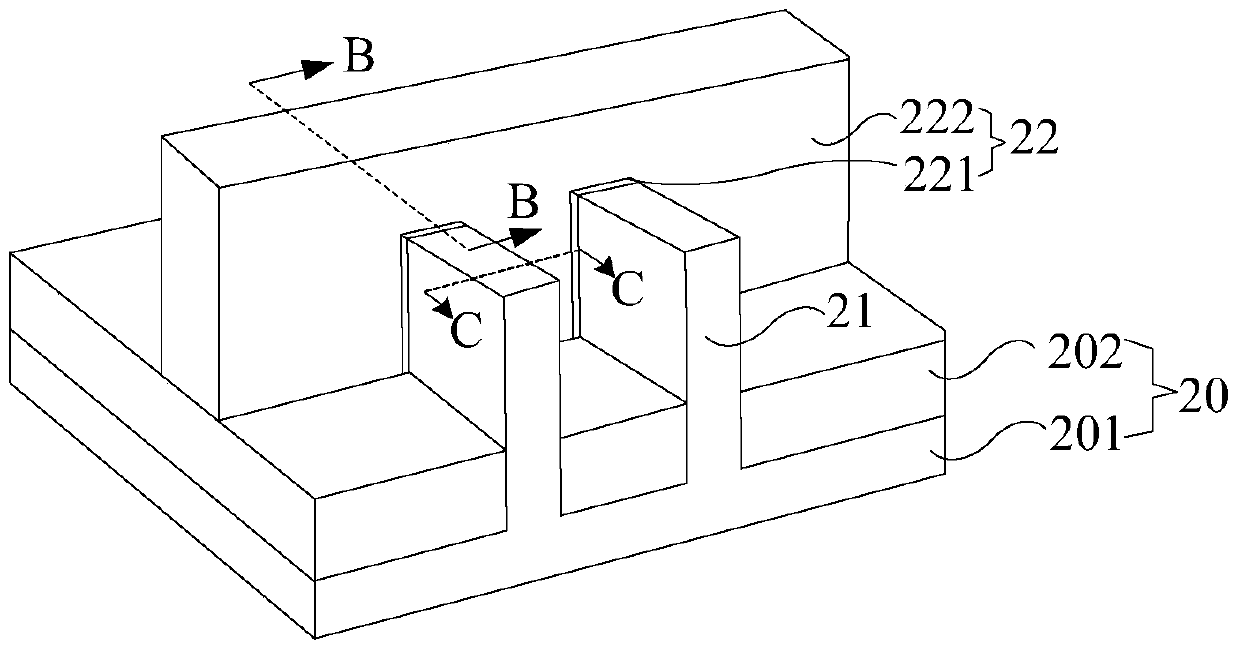

Embodiment Construction

[0046] The inventors found that the reasons for the poor performance of the P-type fin field effect transistor formed by the method of the prior art are:

[0047] The sum of the Schottky barrier value of the P-type fin field effect transistor and the Schottky barrier value of the N-type fin field effect transistor on the same semiconductor substrate is equal to the forbidden band width value of silicon, which is a constant ( 1.12). For N-type fin field effect transistors, when the metal silicide layer is a titanium metal silicide layer, the Fermi level is near the conduction band, which will make the Schottky barrier value of the N-type fin field effect transistor Very low, N-type FinFET performance is good. However, for the P-type fin field effect transistor, when the metal silicide layer is a titanium metal silicide layer, the Schottky barrier value of the P-type fin field effect transistor will be very high. In this way, the parasitic resistance generated by the P-type fin ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com