Generation method of optimal net list for functional simulation of large-capacity FPGA (Field Programmable Gate Array) circuit

A circuit function and large-capacity technology, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve problems such as spending the same time and occupying server resources, so as to improve coverage and meet the needs of simulation , the effect of saving simulation resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0017] In order to save simulation resources and improve the running speed of the simulator. The invention proposes a method for generating an optimal netlist for functional simulation of a large-capacity FPGA circuit.

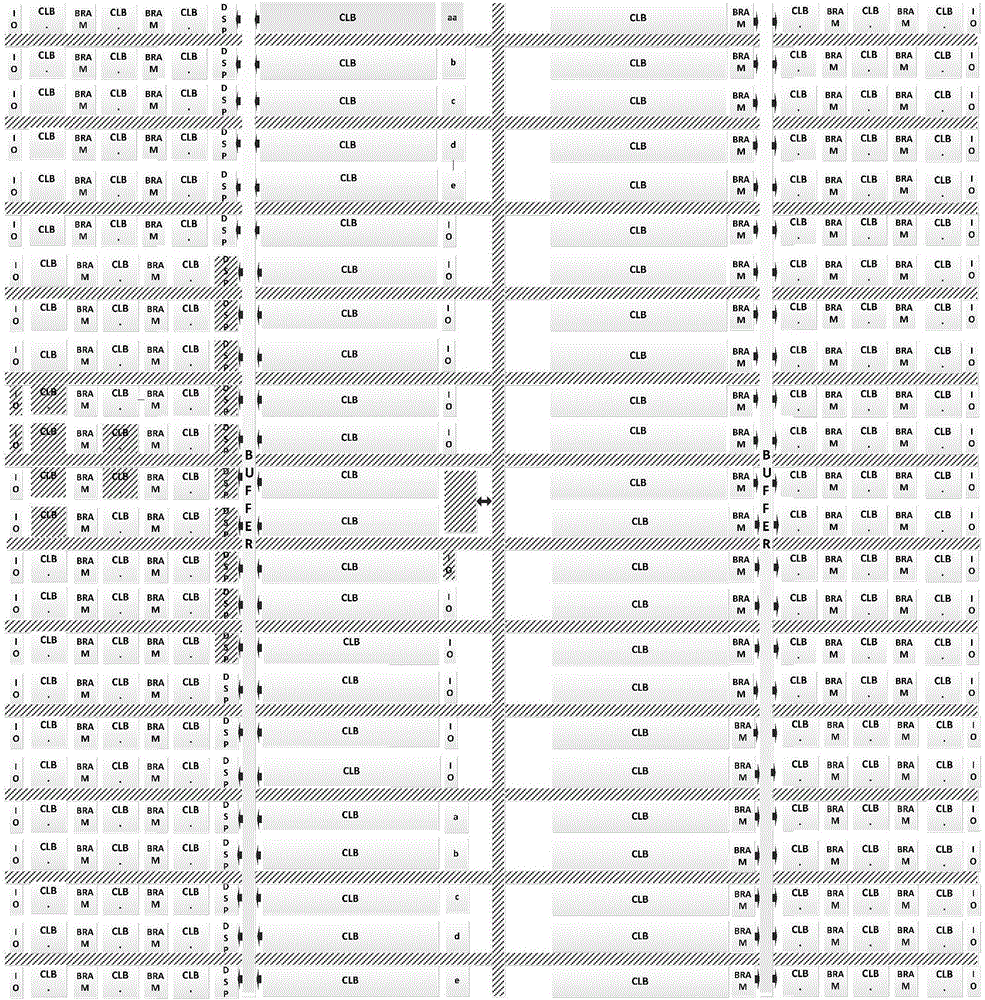

[0018] Such as figure 1 As shown, it is a schematic diagram of the top-level unit structure of a large-capacity FPGA circuit. Since FPGA integrates programmable logic unit (CLB), digital signal processing (DSP), clock management (CMT), storage unit (Block RAM, BRAM), clock module ( CLK), system control module (CTRL), high-speed interface and other units, among which the switch matrix Switch box (SWB) is the interconnection hub connecting CLB, DSP, BRAM, IO, CLK, high-speed interface and other modules. It consists of a large number of The MUX switch (data selector), configuration SRAM (static random access memory) and winding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com