A circuit structure and operation method for realizing chained list pipeline operation

A circuit structure and linked list technology, applied in the direction of memory address/allocation/relocation, etc., to achieve the effect of improving processing bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described below in conjunction with specific examples and accompanying drawings.

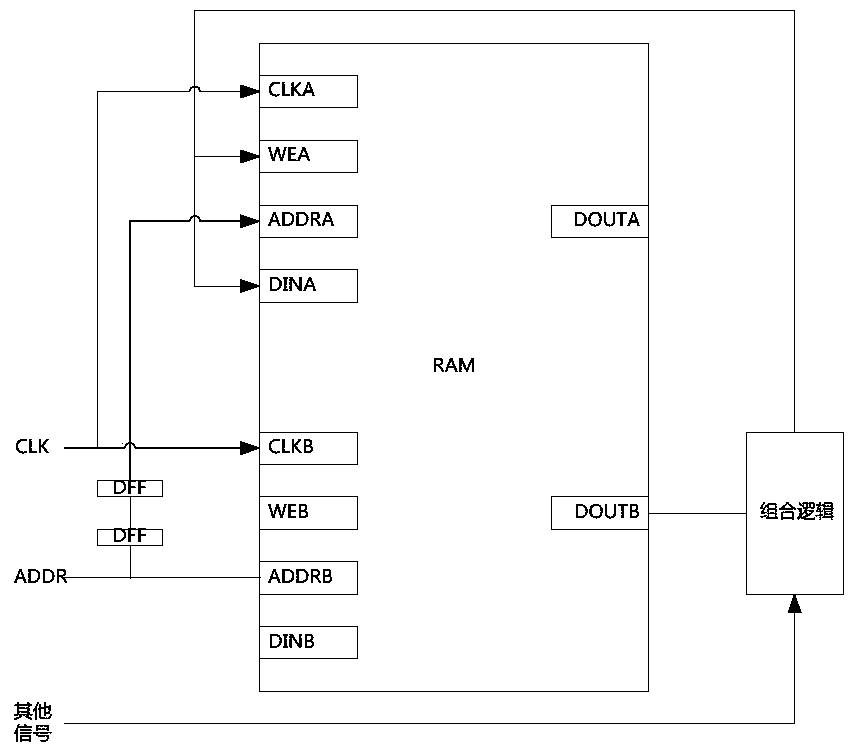

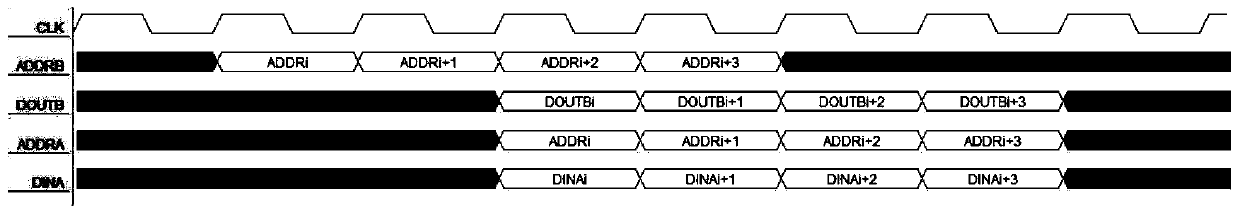

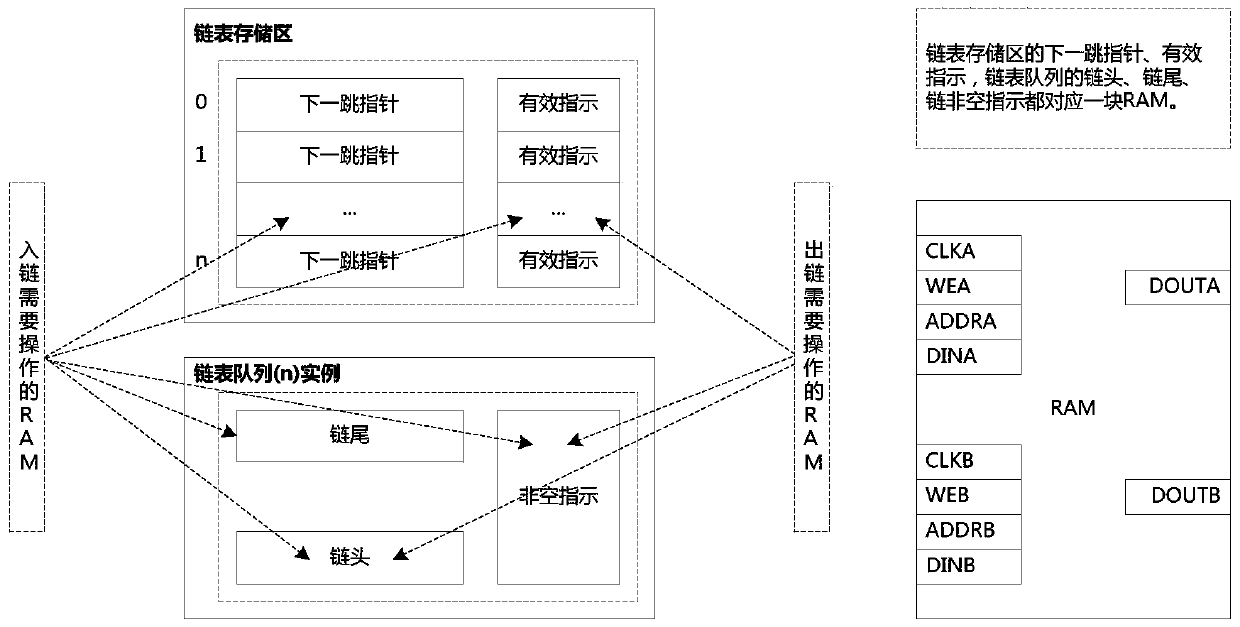

[0042] The present invention provides a circuit structure for realizing the pipeline operation of the linked list, such as Figure 4 As shown, it includes a linked list storage area and a linked list queue, the linked list storage area includes a next hop pointer and a valid indication of the next hop pointer, and the linked list queue includes a chain head, a chain tail, and a non-null indication of the chain head; the next hop pointer The valid indication is represented by 2 bits, denoted as status0[1:0], its 2 bits are respectively represented as status0[0] and status0[1], and status0[0] is defined to be readable and writable on the inbound side and outbound side can only be read, status0[1] is readable and writable on the outbound side, and can only be read on the inbound side; The status is represented by 2 bits, denoted as status1[1:0], its 2 b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com