Wiring board with interposer and dual wiring structures integrated together and method of making the same

A wiring structure and circuit board technology, applied in multilayer circuit manufacturing, printed circuit manufacturing, circuit and other directions, can solve problems such as poor reliability of wafer-level connections, and achieve the goal of avoiding unconnected micro-blind holes and avoiding bending problems Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

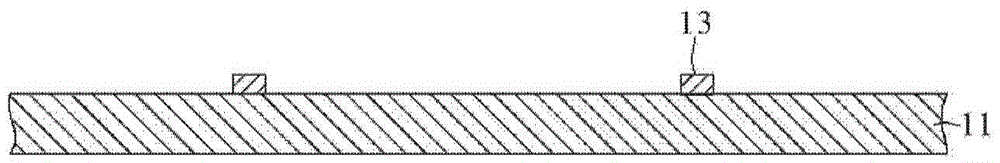

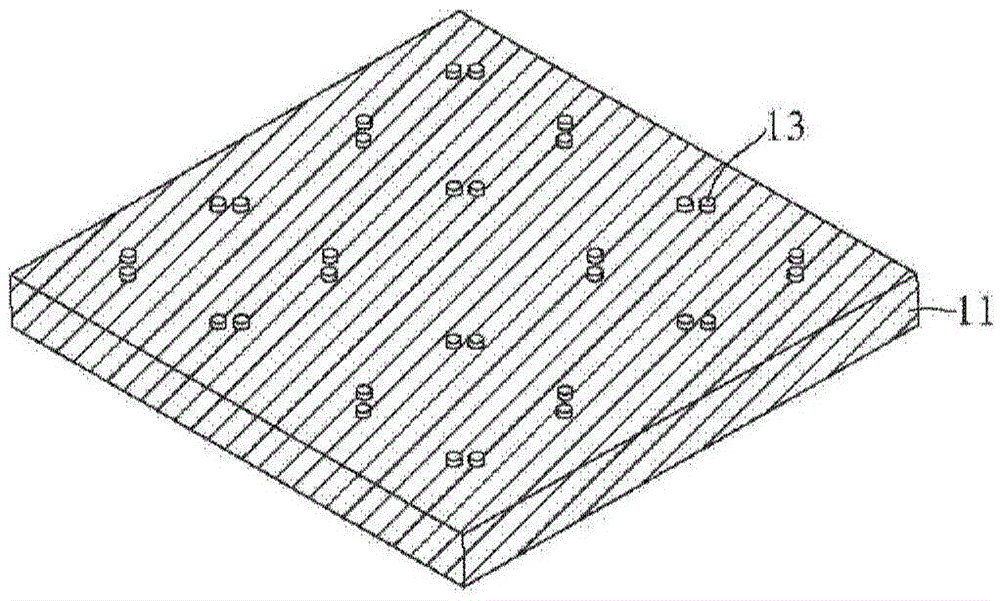

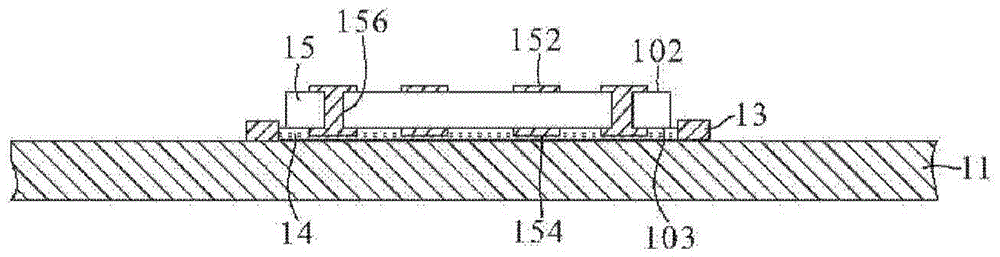

[0104] Figure 1-21 It is a diagram of a manufacturing method of a circuit board in an embodiment of the present invention, which includes an intermediate layer 15 , a first wiring structure 17 , a strengthening layer 20 and a second wiring structure 40 .

[0105] figure 1 and 2 They are respectively a cross-sectional view and a top perspective view of multiple sets of positioning elements 13 on the sacrificial carrier 11 . The sacrificial carrier 11 is typically made of copper, aluminum, iron, nickel, tin, stainless steel or other metals or alloys, but can also be made of any other conductive or non-conductive material. The thickness of the sacrificial carrier 11 is preferably 0.1 mm to 2.0 mm. The positioning member 13 protrudes from the top surface of the sacrificial carrier 11 and has a thickness of 5 to 200 microns. In this embodiment, the sacrificial carrier 11 has a thickness of 1.0 mm, and the positioning member 13 has a thickness of 50 microns. If a conductive sa...

Embodiment 2

[0131] Figure 23-51 It is a diagram of a circuit board manufacturing method according to another embodiment of the present invention, which includes the step of attaching the interposer semi-finished product to a sacrificial carrier.

[0132] For the purpose of brief description, any descriptions in the above-mentioned embodiment 1 that can be used for the same application are incorporated here, and it is not necessary to repeat the same descriptions.

[0133] Figure 23 and 24 They are respectively a cross-sectional view and a bottom perspective view of the substrate 151 , which includes a first surface 101 , an opposite second surface 103 , and a blind hole 104 formed on the second surface 103 . The substrate 151 may be made of silicon, glass or ceramics, and has a thickness of 50 μm to 500 μm. The blind holes 104 have a depth of 25 microns to 250 microns. In this embodiment, the substrate 151 is a silicon wafer and has a thickness of 200 microns, and the blind hole 104...

Embodiment 3

[0159] Figures 52-56 It is a diagram of a circuit board manufacturing method according to another embodiment of the present invention, which does not use a carrier film, and the second wiring structure is further electrically coupled to the strengthening layer as a ground connection.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com