Formation method of semiconductor structure

A semiconductor and graphics technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of poor semiconductor pattern topography resolution, inconsistent semiconductor pattern shape, etc., and achieve the effect of improving shape resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

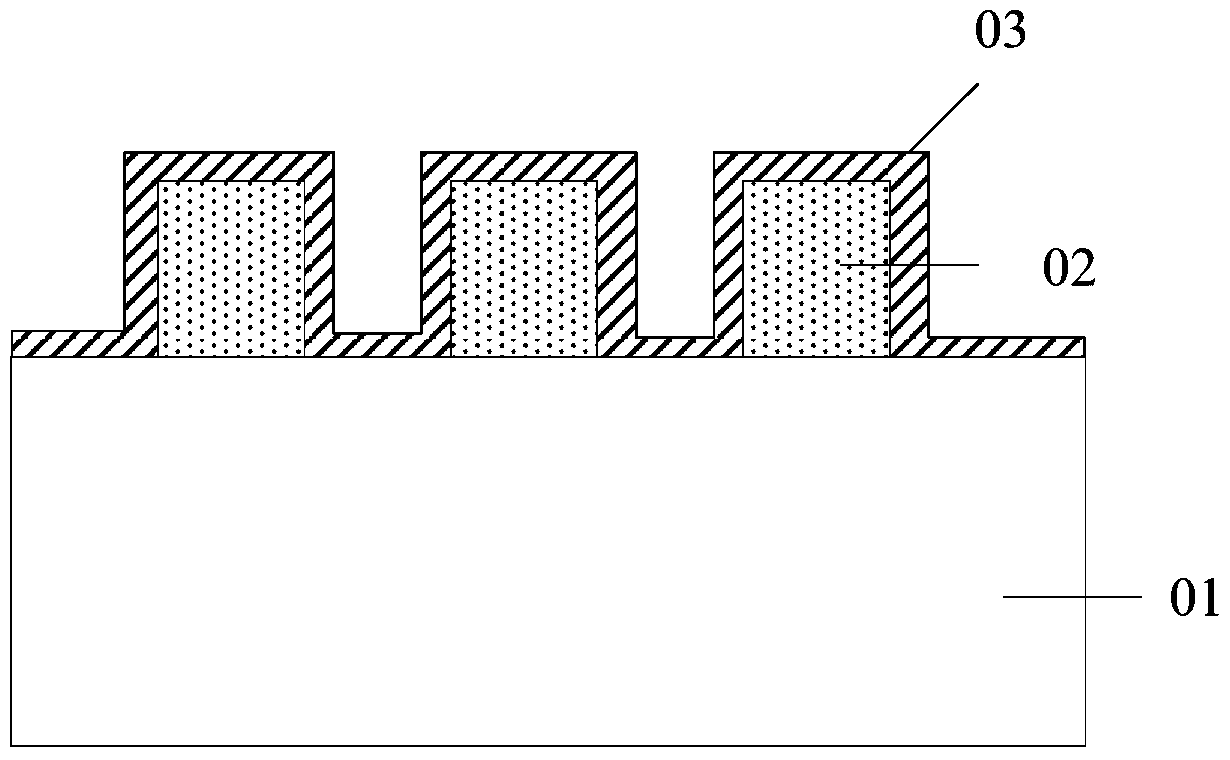

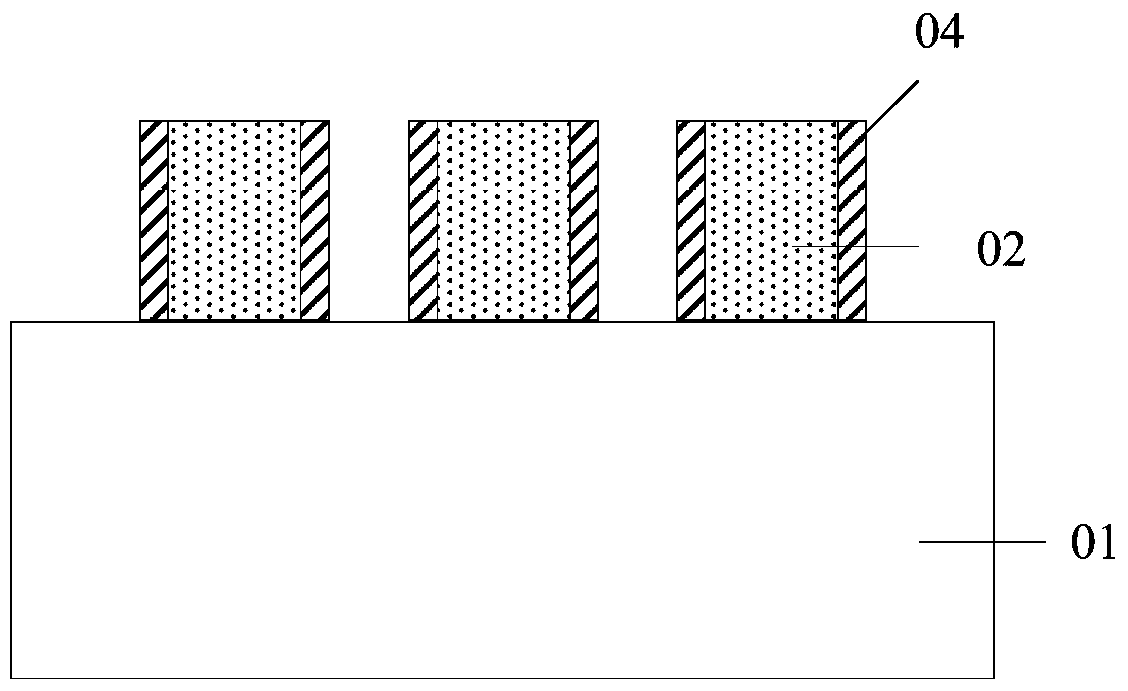

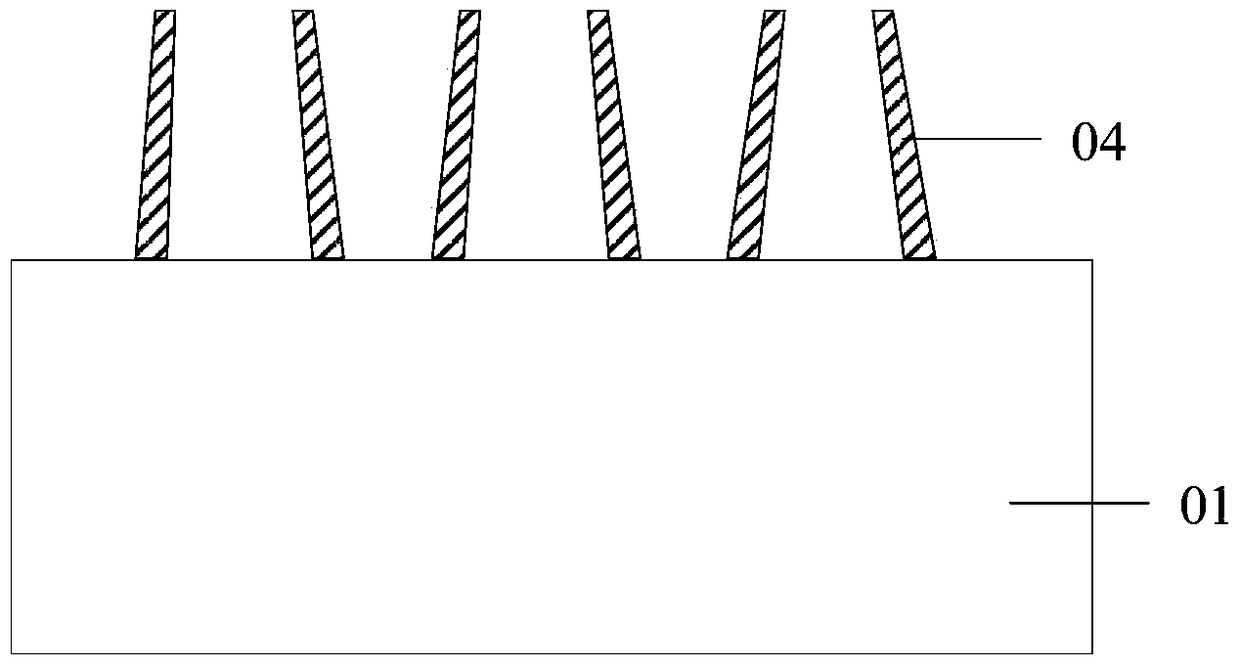

[0032] In the prior art self-aligned double exposure, the sidewall is prone to inclination due to the effect of stress, and the substrate is etched with the inclined sidewall as a mask, and the semiconductor pattern formed has poor morphology, and the shape of the semiconductor pattern Easily distorted compared to the desired shape. Analyze the reason why the side wall is prone to tilt: in the step of depositing the side wall material layer, the stress in the side wall material layer is relatively large, after the side wall is formed, the stress inside the side wall is relatively large, and it is located at different positions on the substrate The stress direction of the side wall may be different, which may be tensile stress or compressive stress. After the sacrificial figure is removed, the side wall may be inclined towards the original position of the sacrificial figure, or may be inclined towards the original position of the sacrificial figure.

[0033] In order to solve t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com