Simulation platform design method based on Power PC SoC framework

A technology of simulation platform and design method, which is applied in computing, special data processing applications, instruments, etc., can solve problems such as the inability to evaluate the quality of SoC architecture, and the accuracy of rough modeling, so as to shorten the time-to-market cycle, speed up the design process, shorten The effect of the development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The simulation platform design method based on the PowerPCSoC architecture of the present invention will be described in detail below in conjunction with the embodiments and the accompanying drawings.

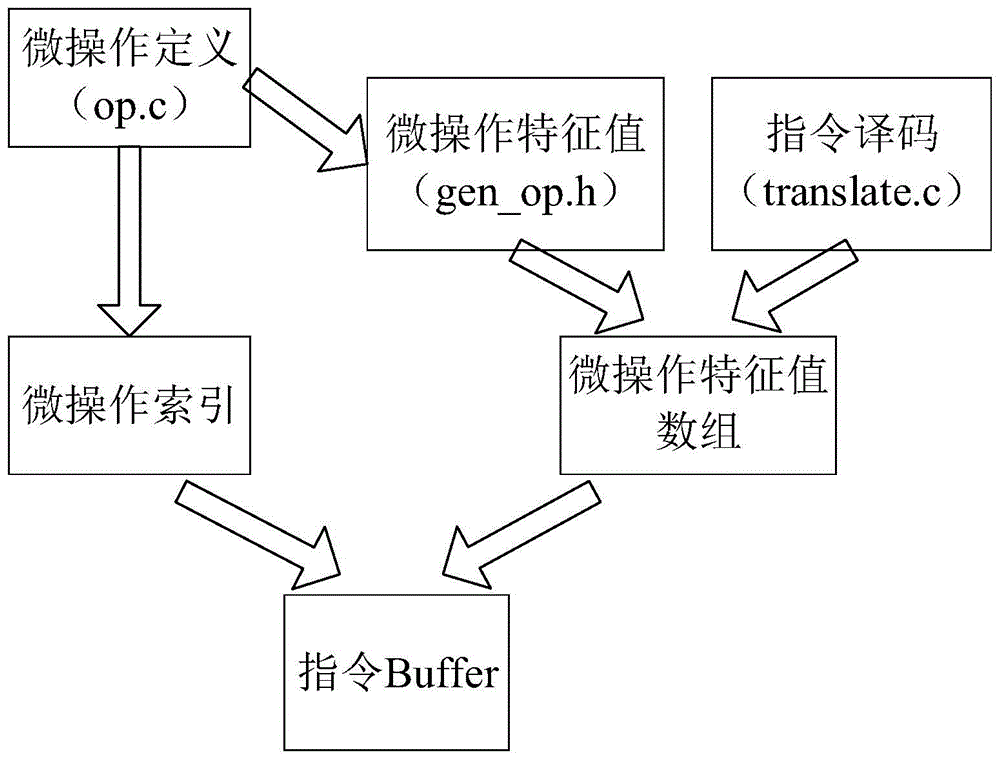

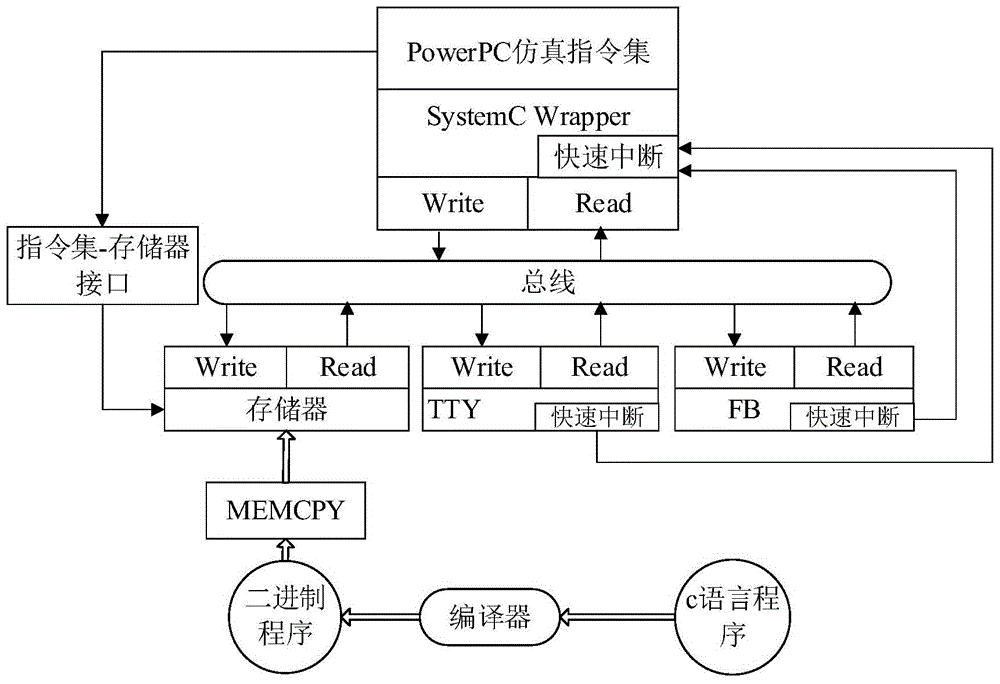

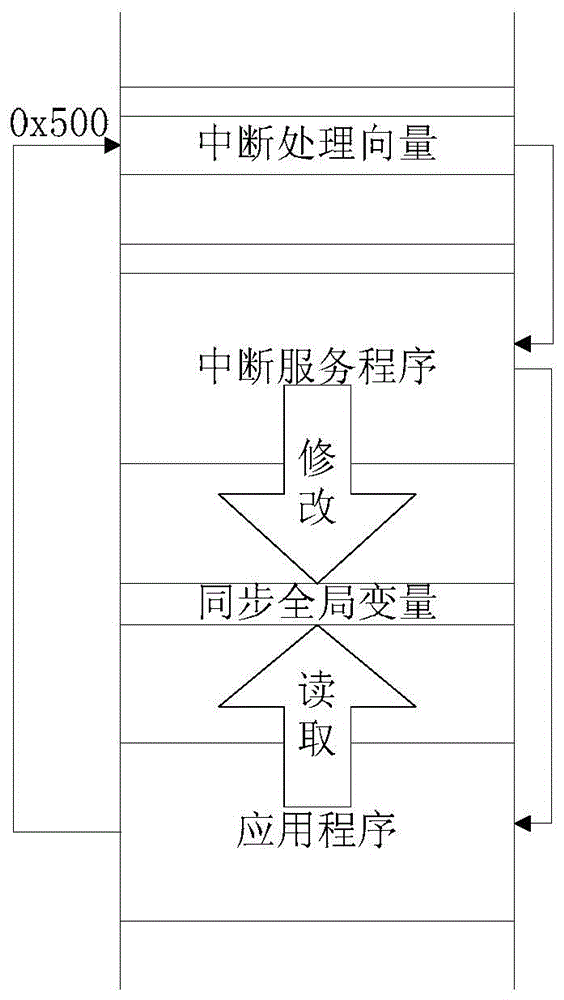

[0028] The simulation platform design method based on the PowerPCSoC architecture of the present invention combines the advantages of two methods based on transaction-level modeling and virtual machine technology, and uses the method of dynamic binary translation of the QEMU virtual machine to implement the instruction set simulator for PowerPC405 series processors. design. And based on the SystemC transaction-level modeling method, the precise modeling of key components in PowerPCSoC such as the slave device module, interrupt module, and DCR register is completed, and the hardware behavior of the SoC is accurately simulated. Finally, based on the designed PowerPCSoC simulation platform, the software development process is designed, and the software-hardware co-design of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com