Thin film transistor and preparation method therefor, and array substrate

A thin film transistor and carbon nanotube technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., to achieve the effect of improving stability and avoiding adverse effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

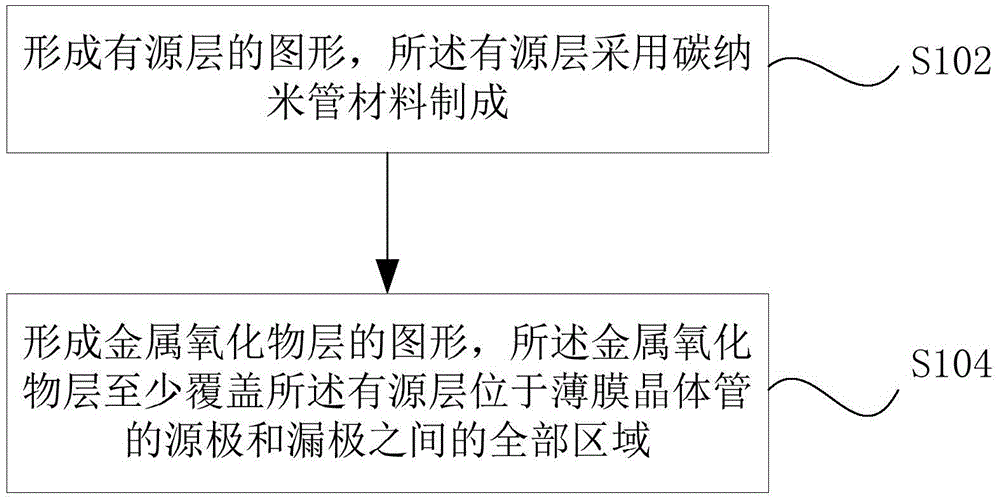

[0026] Based on this, an embodiment of the present invention provides a method for manufacturing a thin film transistor. figure 1 is a flow chart of a method for preparing a thin film transistor according to an embodiment of the present invention, such as figure 1 As shown, the process includes the following steps (step S102-step S104):

[0027] Step S102, forming the pattern of the active layer, the active layer is made of carbon nanotube material;

[0028] Step S104 , forming a pattern of a metal oxide layer, the metal oxide layer covering at least the entire area of the active layer between the source and the drain of the thin film transistor.

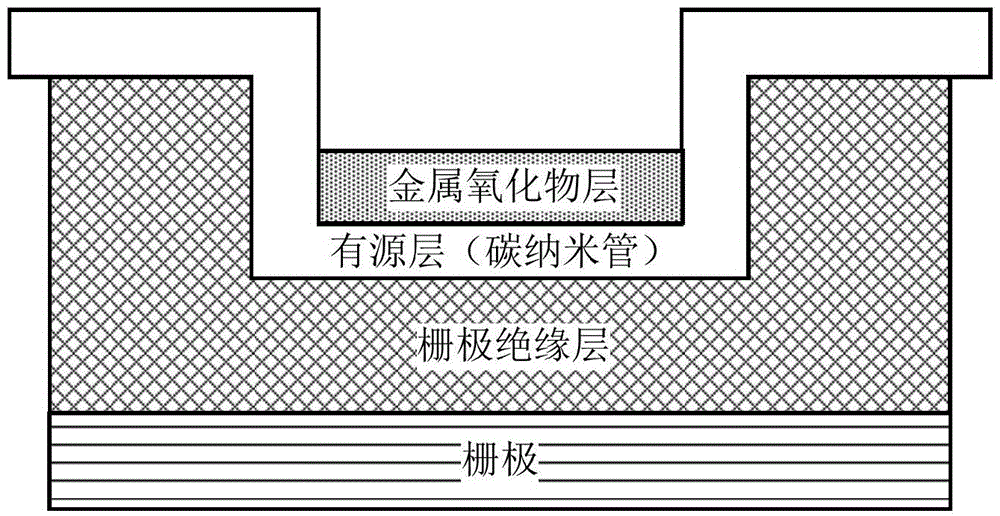

[0029] For the process of preparing the thin film transistor, firstly, a gate can be formed on a glass substrate, then a gate insulating layer can be formed on the gate, and then the pattern of the active layer can be formed on the gate insulating layer by using carbon nanotube material, and then Form the metal oxide layer and t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com