Functional verification method and platform for ddr3 SDRAM controller

A function verification and controller technology, applied in instruments, static memory, etc., can solve problems such as limiting DDR3 SDRAM read and write performance, achieve the effect of convenient maintenance and upgrade, convenient maintenance and upgrade, and reduce the chance of omissions and errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

test Embodiment 11

[0033] Test case 11, used to detect the correctness of user read and write operations, specific user interface timing or signals;

[0034] The port monitoring module 12 designed with hierarchical and object-oriented technology is used to detect the correctness of the DDR3 SDRAM port signal.

[0035] In some embodiments, the port monitoring module 12 in the above-mentioned embodiments is used to encapsulate the signal of the DDR3 SDRAM port into a command service in units of commands, monitor and analyze the command service according to the state table, and determine the DDR3 SDRAM port signal according to the analysis result correctness.

[0036] In some embodiments, the port monitoring module 12 in the above embodiments is also used to set the main content, logical structure, member variables and member methods of the command service.

[0037] In some embodiments, the logic structure in the above embodiments is a tree logic structure including commands, non-MRS commands, arr...

no. 2 example

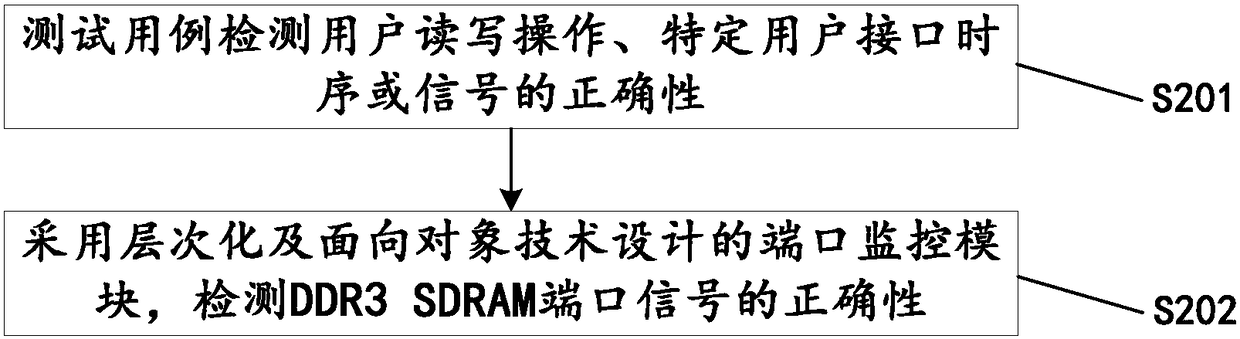

[0041] figure 2 The flow chart of the function verification method provided by the second embodiment of the present invention is composed of figure 2 It can be seen that, in the present embodiment, the function verification method for the DDR3 SDRAM controller provided by the present invention comprises the following steps:

[0042] S201: The test case detects the correctness of user read and write operations, specific user interface timing or signals;

[0043] S202: A port monitoring module designed with layered and object-oriented technology is used to detect the correctness of the DDR3 SDRAM port signal.

[0044]In some embodiments, the port monitoring module in the foregoing embodiments detects the correctness of the DDR3 SDRAM port sequence: the signal of the DDR3 SDRAM port is encapsulated as a command service in units of commands, and the command service is monitored and analyzed according to the state table, according to The analysis result confirms the correctness...

no. 3 example

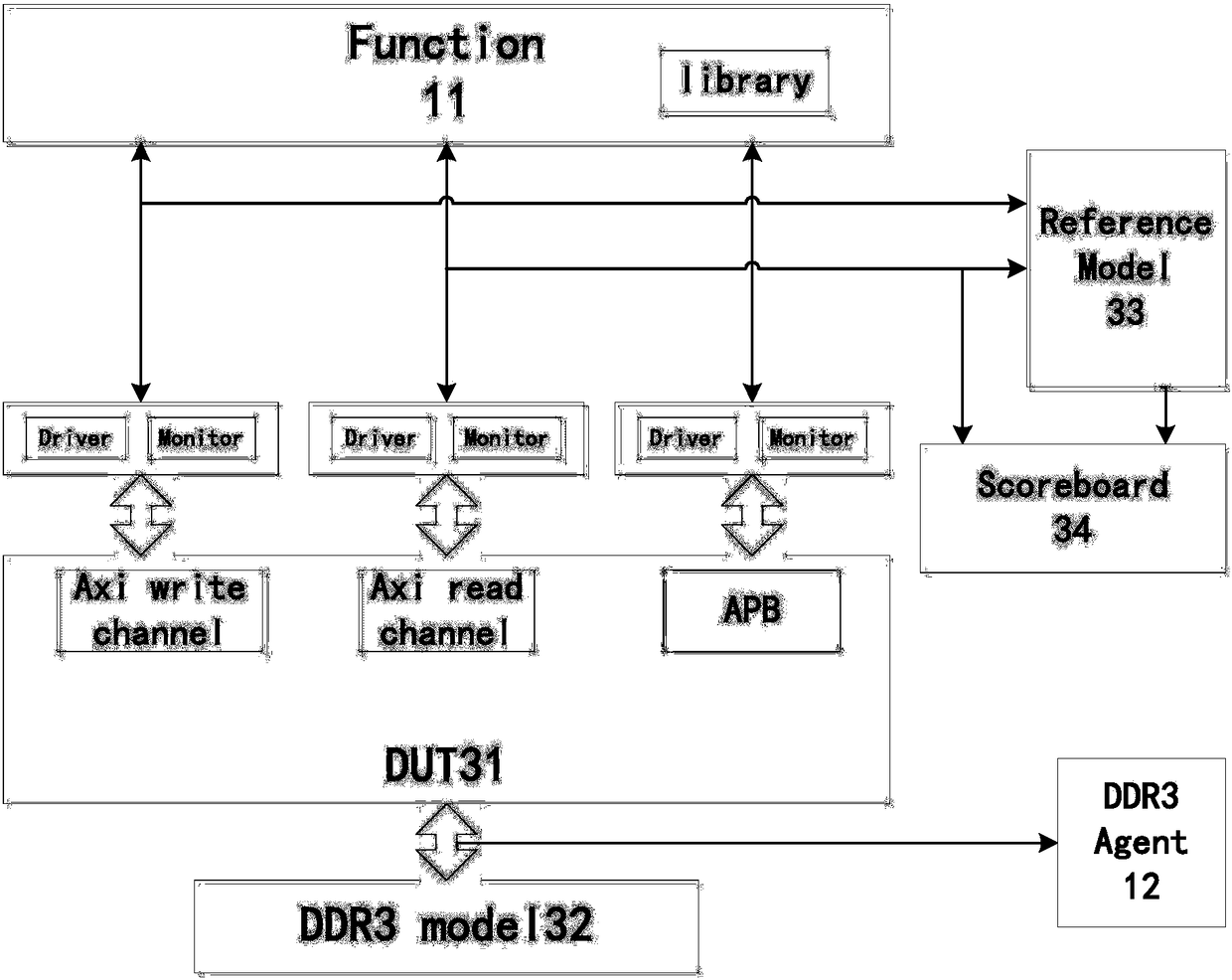

[0050] The present invention will be further explained in combination with specific application scenarios.

[0051] The agreement stipulates many timing constraints of DDR3 SDRAM in operation. These timings are complex and easy to omit during verification. Therefore, how to effectively find an architecture that can effectively organize these constraints in time and space is an important issue. question. The role of the verification platform in chip verification determines that the code of the verification platform should be easy to maintain and robust; in addition, considering the future development of the DDR series, it also needs to have good adaptability to facilitate future possible new additions. Function, only need to add and modify a small amount of code to upgrade the verification platform.

[0052] Based on the above-mentioned technical status, this embodiment provides a test platform using System Verilog language programming. The overall structure of the test platfo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com