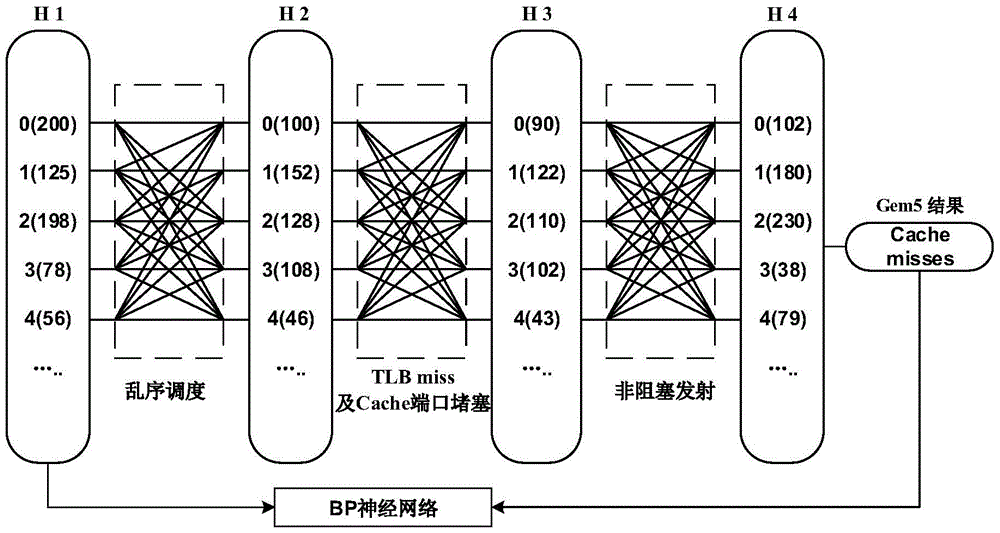

Artificial neural network-based out-of-order processor Cache memory access performance evaluation method

An artificial neural network and out-of-order processor technology, applied in neural learning methods, biological neural network models, electrical digital data processing, etc., can solve the problem of low precision and achieve the effect of accelerating speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Below in conjunction with accompanying drawing and specific embodiment, further illustrate the present invention, should be understood that these examples are only for illustrating the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various aspects of the present invention All modifications of the valence form fall within the scope defined by the appended claims of the present application.

[0033] A kind of out-of-order processor Cache performance evaluation method based on artificial neural network, comprises the following steps:

[0034] Step 1, simulate and obtain the memory access out-of-order execution flow of the first 30% of the execution time of the target program; reorder the out-of-order execution flow according to the Gem5 instruction fetch sequence number to obtain the sequential execution flow of memory access; design the stack distance algo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com