Shifting register, grid-driven circuit and display device

A shift register and driving signal technology, applied in static memory, digital memory information, instruments, etc., can solve problems such as display panel flickering, different scanning signals, and waveform deformation of scanning signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

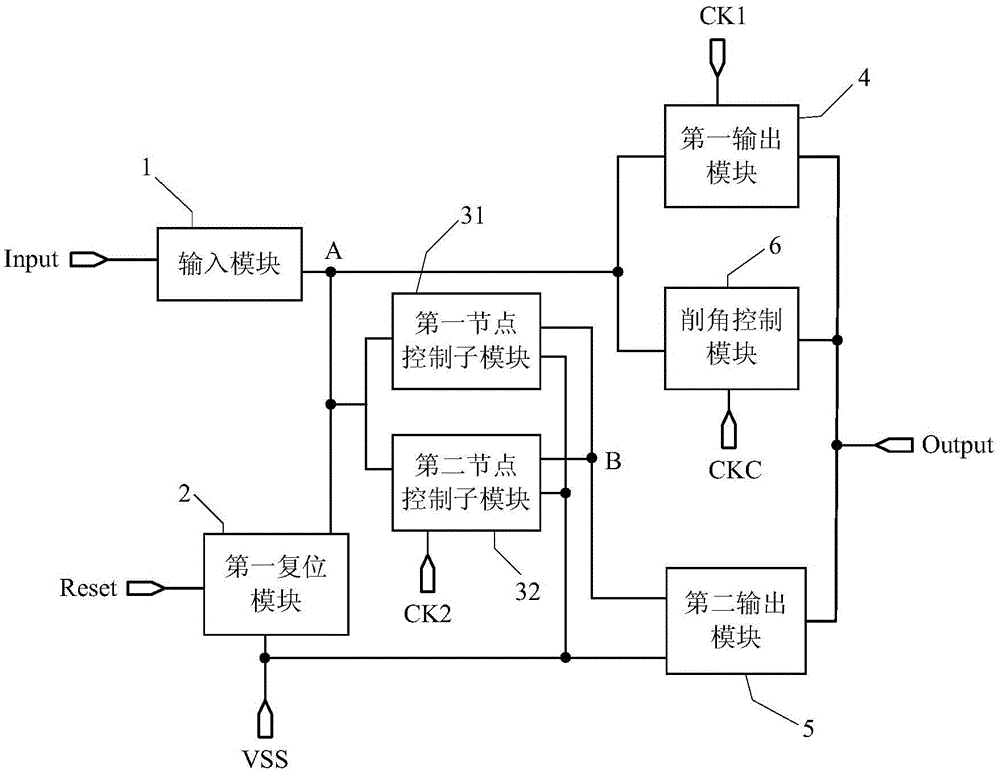

Embodiment 1

[0124] by Figure 3b The structure of the shift register shown is taken as an example to describe its working process, wherein, in Figure 3b In the shift register shown, all the switch transistors are N-type switch transistors, and each N-type switch transistor is turned on under the action of a high potential, and is turned off under the action of a low potential; the potential of the reference signal terminal VSS is a low potential, and the corresponding The input and output timing diagram is as follows Figure 5a Shown, specifically, select as Figure 5a There are five stages in the shown input-output timing diagram, the first stage T1 , the second stage T2 , the third stage T3 , the fourth stage T4 and the fifth stage T5 .

[0125] In the first phase T1, Input=1, Reset=0, CK1=0, CK2=1, CKC=1.

[0126] Because Reset=0, so the seventh switch transistor M7 and the eleventh switch transistor M11 are both cut off; because Input=1, so the sixth switch transistor M6 is turned...

Embodiment 2

[0141] by Figure 4b The structure of the shift register shown is taken as an example to describe its working process, wherein, in Figure 4b In the shift register shown, all the switching transistors are P-type switching transistors, and each P-type switching transistor is turned on under the action of a low potential, and is turned off under the action of a high potential; the potential of the reference signal terminal VSS is a high potential, and the corresponding The input and output timing diagram is as follows Figure 5b Shown, specifically, select as Figure 5b There are five stages in the shown input-output timing diagram, the first stage T1 , the second stage T2 , the third stage T3 , the fourth stage T4 and the fifth stage T5 .

[0142] In the first stage T1, Input=0, Reset=1, CK1=1, CK2=0, CKC=0.

[0143] Because Reset=1, both the seventh switching transistor M7 and the eleventh switching transistor M11 are turned off; because Input=0, the sixth switching transis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com