Phase locking method based on FPGA and phase-locked loop adopting same

A phase-locked and component technology, which is applied in the automatic control of power, electrical components, etc., can solve the problem of low detection accuracy of the phase-locked loop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

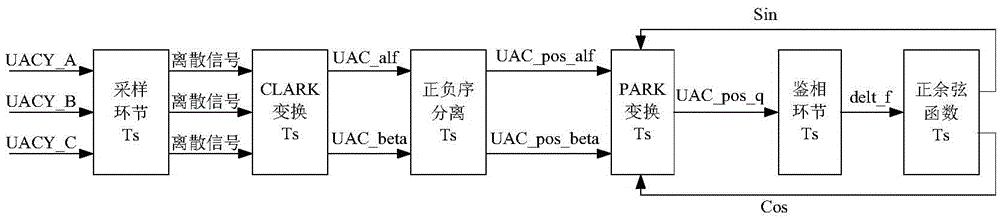

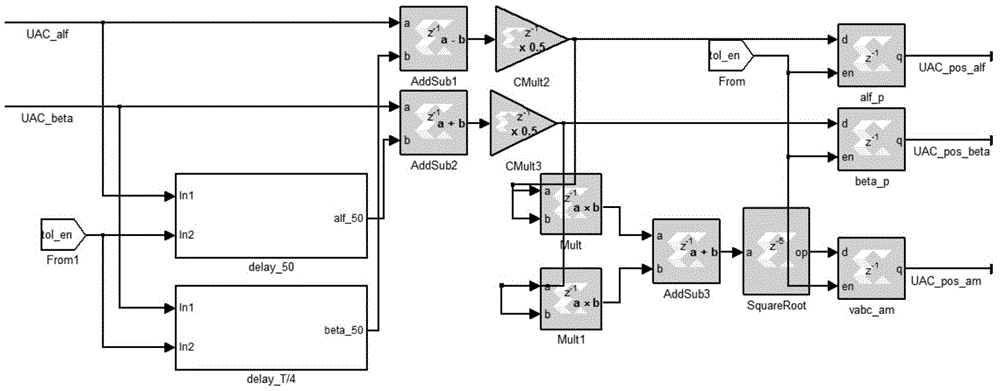

[0045] Based on the FPGA-based phase-locking method, the main process of realizing the method of the present invention in this embodiment is as follows: collecting the grid-side voltage in the system, CLARK transformation, extraction of positive and negative sequence components, PARK transformation and phase identification link, and calculation of voltage phase Measured value; specific steps are as follows:

[0046] Step (1), collecting grid-side voltage in the system:

[0047] Set the program execution step T_step, and sample the grid-side voltage in the flexible DC input system. For each sampling, use the counter to add 1 to T_step, and complete the sampling of the entire program within the program task period Ts to ensure that all function blocks are Execute once in the set order within Ts.

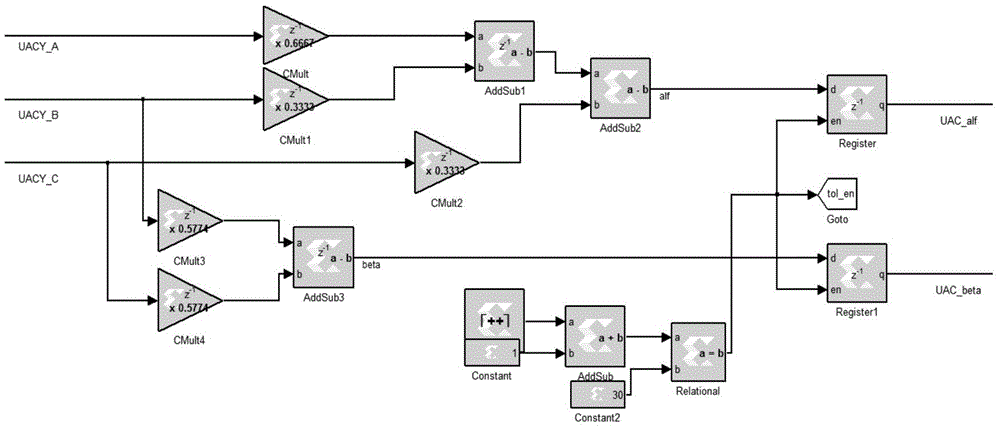

[0048] Step (2), CLARK transformation:

[004...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com