Super-junction device and manufacturing method therefor

A technology of super junction devices and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as circuit damage, loop oscillation, application system current and voltage overshoot, etc., and achieve the minimum increase in capacitance , the effect of increasing the overall capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0072] Embodiment 1 of the present invention super junction device:

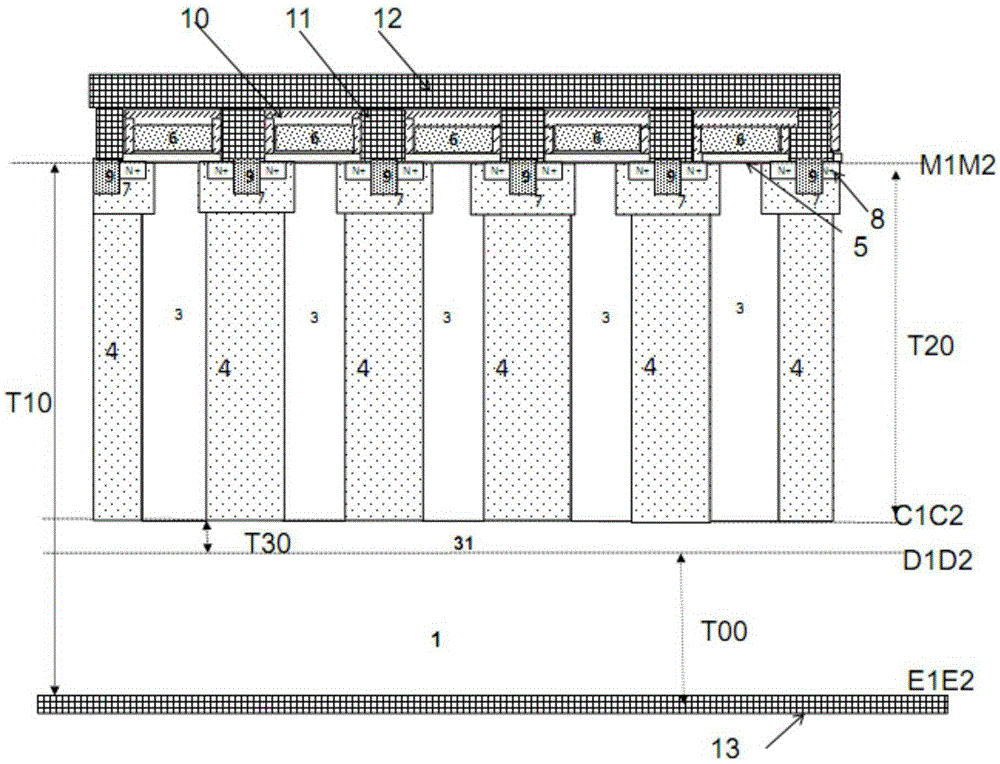

[0073] Such as Figure 5 As shown, it is a cross-sectional view of a super-junction device in an embodiment of the present invention; a super-junction device in an embodiment of the present invention is described by taking a planar gate super-junction N-type MOSFET as an example, and a planar-gate super-junction P-type MOSFET is used to dope the device It can be obtained by replacing the P-type and N-type regions, and the planar gate super-junction P-type MOSFET will not be described in detail.

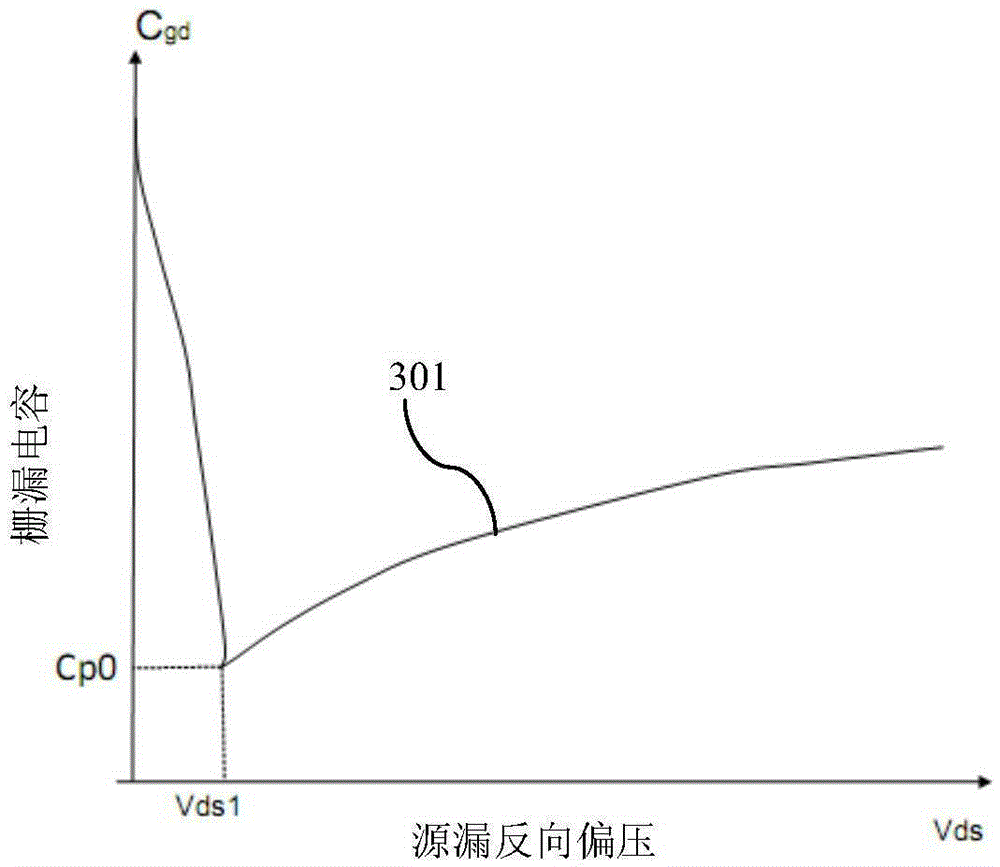

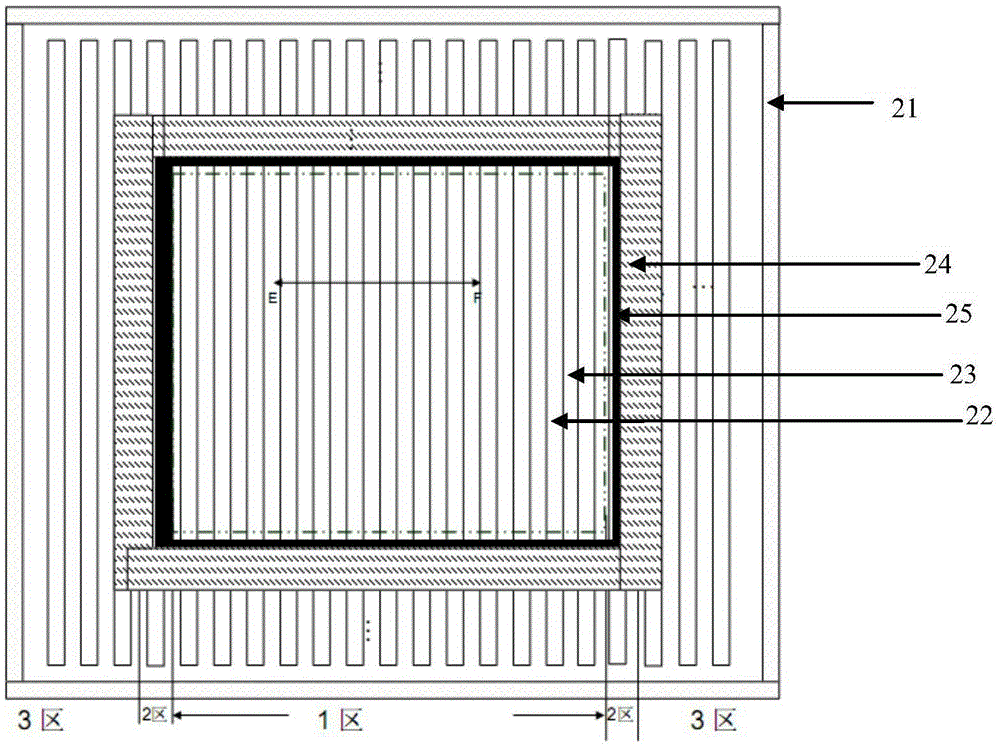

[0074] Such as image 3 As shown, it is a top view of a super junction device according to the embodiment of the present invention Figure 1 A general superjunction structure includes a charge flow region, a terminal region that bears a reverse bias voltage laterally, and a transition region between the charge flow region and the terminal region, and the terminal region surrounds the periphery of the charge flow r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com