Digital self-calibration circuit and method of successive approximation analog-to-digital converter

An analog-to-digital converter and successive approximation technology, applied in the direction of analog/digital conversion calibration/testing, can solve the problems of increasing design area, reducing design performance, etc., and achieve the effect of reducing delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

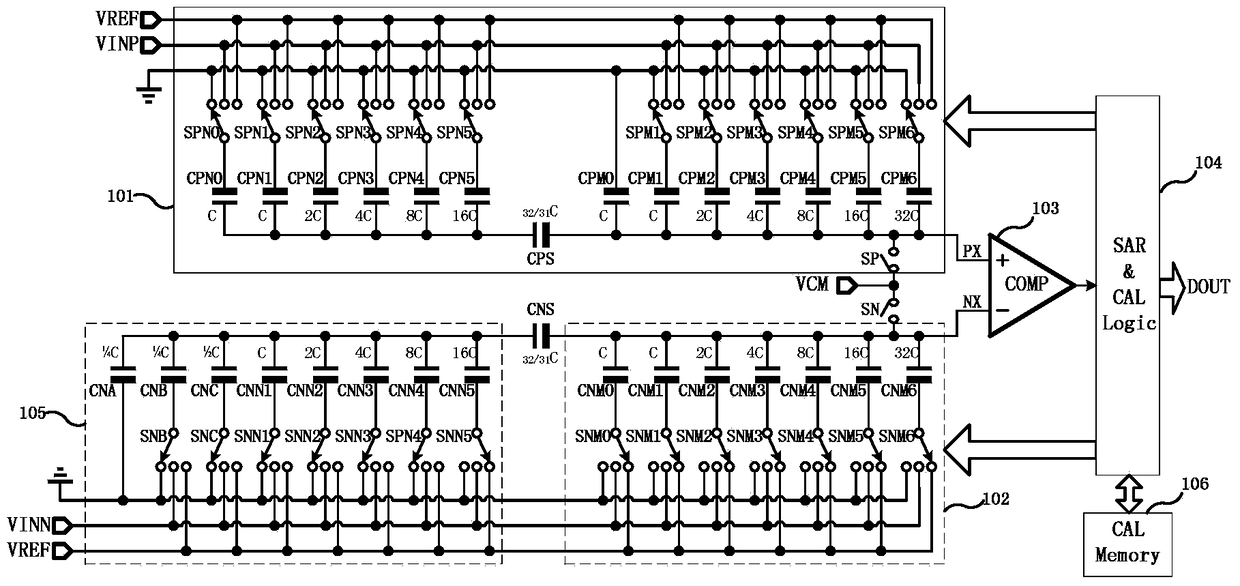

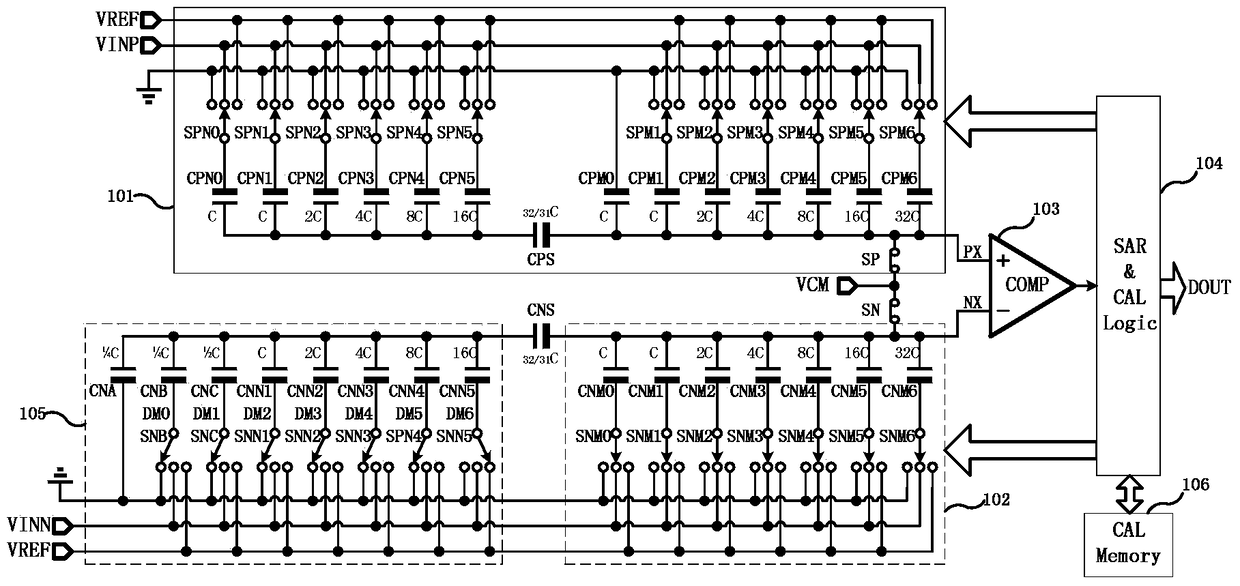

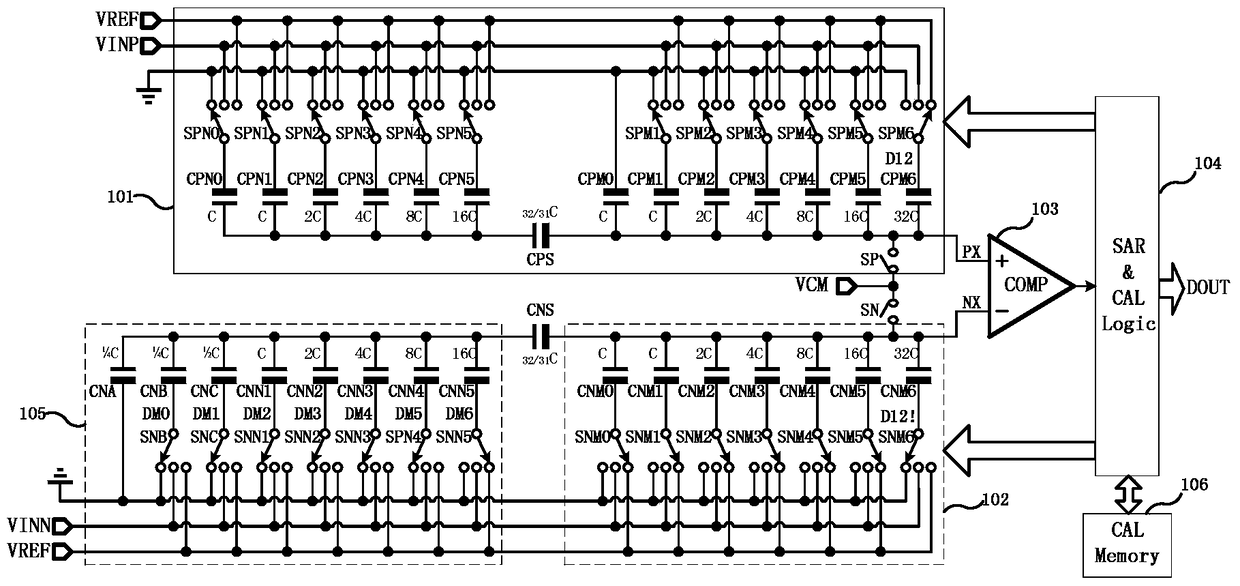

[0049] 为了便于理解,现以一个具体的逐次逼近型模数转换器为例说明本发明实施例的数字自校准电路,具体的逐次逼近型模数转换器如 figure 1 所示;逐次逼近模数转换器包括第一电容阵列101、第二电容阵列102、校准电容阵列105、比较器(COMP)103、控制逻辑电路(SAR&CAL Logic)104和存储器(CAL Memory)106。由第一电容阵列101和第二电容阵列102组成权重电容阵列。

[0050] 所述第一电容阵列101的输出端PX连接到所述比较器103的第一输入端且通过一切换开关SP连接到共模电平VCM,所述第二电容阵列102的输出端NX连接到所述比较器103的第二输入端且通过一切换开关SN连接到共模电平VCM,由所述第一电容阵列101和所述第二电容阵列102组成伪差分电容阵列。

[0051] 所述第一电容阵列101包括第一段子电容阵列和一个以上的低位段子电容阵列,所述第一段子电容阵列为位数比各所述低位段子电容阵列都高。

[0052] 所述第一段子电容阵列包括多位电容,各所述低位段子电容阵列包括多位电容,所述第二电容阵列102的电容位数比所述第一段子电容阵列的电容位数多一个,所述第二电容阵列102的最高位电容到次低位电容依次和相同位的所述第一段子电容阵列的电容大小相等并组成差分权重位电容;所述第二电容阵列102的最低位电容和次低位电容大小相等。

[0053] 模数转换过程中,首先从所述第一段子电容阵列的最高位到最低位进行逐位的差分权重位的模数转换,所述第一段子电容阵列的最低位差分权重位转换完成后,将所述最低位差分权重位码值转换成过渡码值;当所述最低位差分权重位码值为1时,所述过渡码值使所述第二电容阵列102的次低位电容和最低位电容都接地;当所述最低位差分权重位码值为0时,所述过渡码值使所述第二电容阵列102的次低位电容和最低位电容都接参考电压VREF。

[0054] 所述过渡码值转换完成后,由所述第一段子电容阵列的最低位电容和所述低位段子电容阵列的电容组成单端权重位模式电容阵列并进行单端权重位的转换。

[0055] 所述校准电容阵列105包括多位电容,所述校准电容阵列105的输出端和所述第二电容阵列102的输出端通过耦合电容CNS连接,所述校准电容阵列105用于对所述伪差分电容阵列的电容的失配...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com