Software phase-locked loop applicable to nonideality power grid condition

A software phase-locked loop, non-ideal technology, applied in electrical components, circuit devices, AC network circuits, etc., can solve problems such as loss of power signal control capability, protection system tripping, and large harmonic content

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

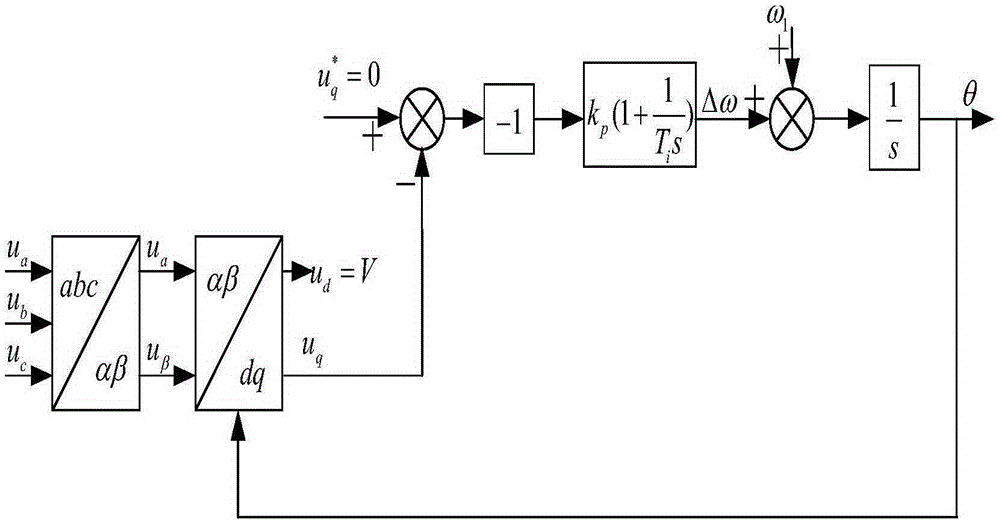

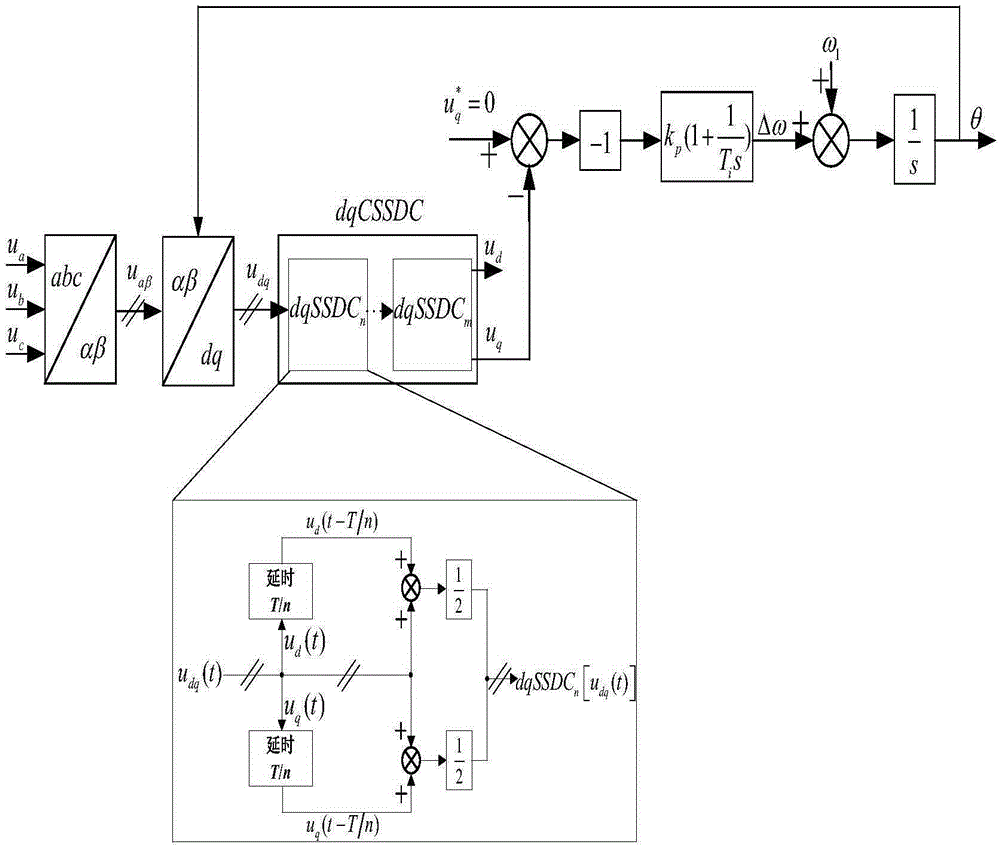

[0102] Such as figure 2 As shown, under the dq coordinates, the control strategy for eliminating harmonics is as follows:

[0103] (a) The three-phase grid voltage is transformed by 3 / 2 rotation to obtain the orthogonal voltage value μ in the stationary coordinate system α , μ β ;

[0104] (b) According to the estimated grid angle to μ α , μ β Do a synchronous rotation transformation to get μ d , μ q ;

[0105] (c) Define the SSDC operator under dq coordinates as dqSSDC n [ v ( t ) ] = 1 2 [ v ( t ) + v ( t - T n ] ;

[0106] (d) μ obtained by synchronous rotation transformation d , μ q Transform the SSDC operator in the dq coordinates...

Embodiment 2

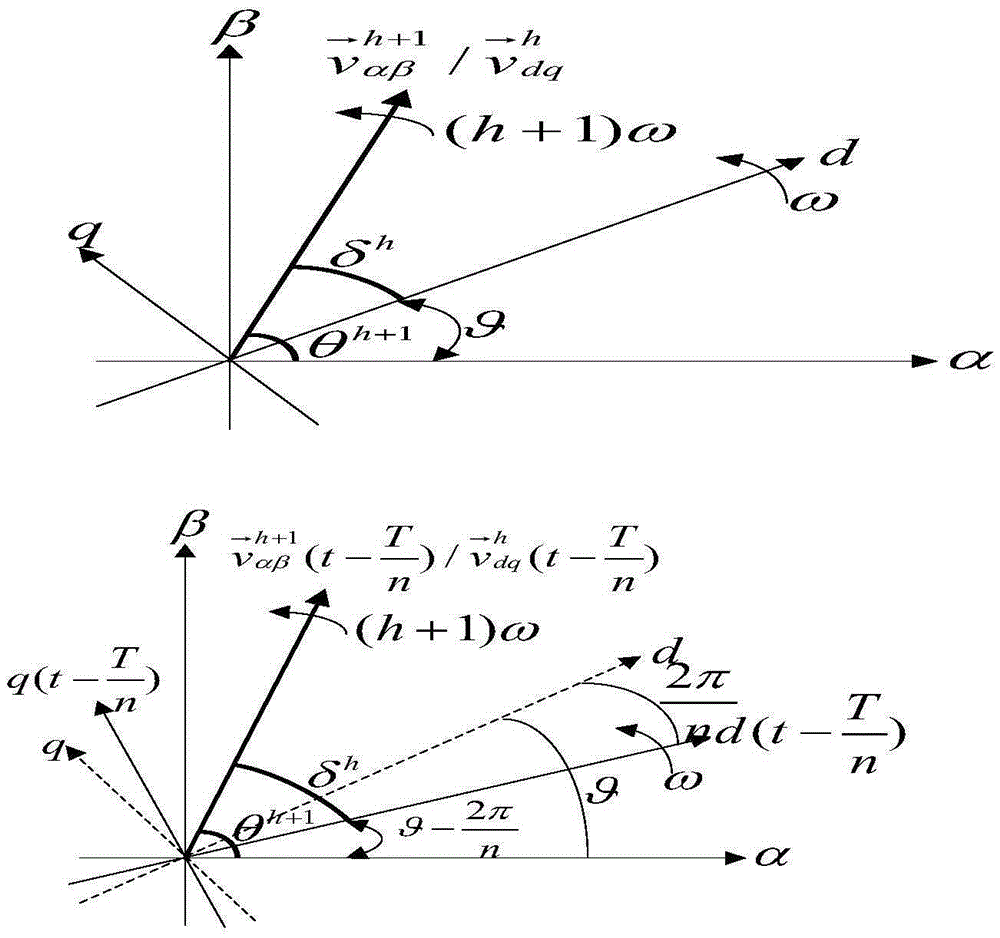

[0109] Such as image 3 , Figure 4 As shown, under the αβ coordinates, the control strategy for eliminating harmonics is as follows:

[0110] (a) Transform the dqSSDC operator to the αβ coordinate system by coordinate transformation, and the harmonic space vector in the dq coordinate system The corresponding quantity in the αβ coordinate system is The transformed angle is The corresponding quantity in the αβ coordinate system is The transformed angle is

[0111] (b) The three-phase grid voltage is transformed by 3 / 2 rotation to obtain the orthogonal voltage value μ in the stationary coordinate system α , μ β ;

[0112] (c) Define the SSDC operator in the αβ coordinates as

[0113] αβSSDC n [ v → α β h ( t ) ] = 1 2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com