Semiconductor structure and formation method thereof

A technology of semiconductor and nanostructure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of chip integration limit, short channel effect, leakage current power increase, etc. Flow carrier mobility and the effect of increasing the channel area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background technology, in the prior art, as the size of semiconductor devices is gradually reduced, various adverse effects restrict the further reduction of device size. How to use high-performance one-dimensional nanostructures to form transistors with better performance is an urgent problem to be solved. The problem.

[0034] This embodiment provides a method for forming transistors and complementary transistors using one-dimensional nanostructures to form transistors with higher performance and higher integration.

[0035]In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

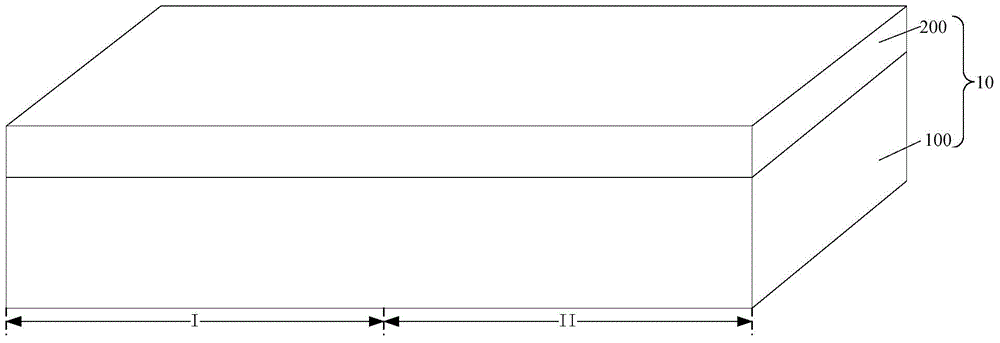

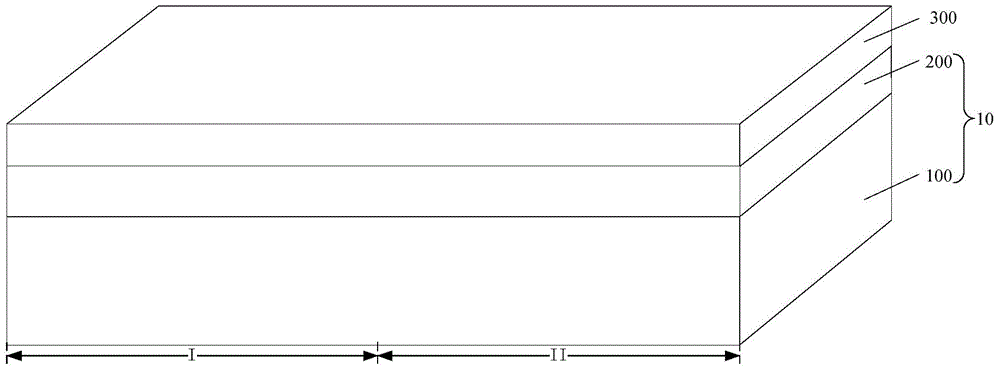

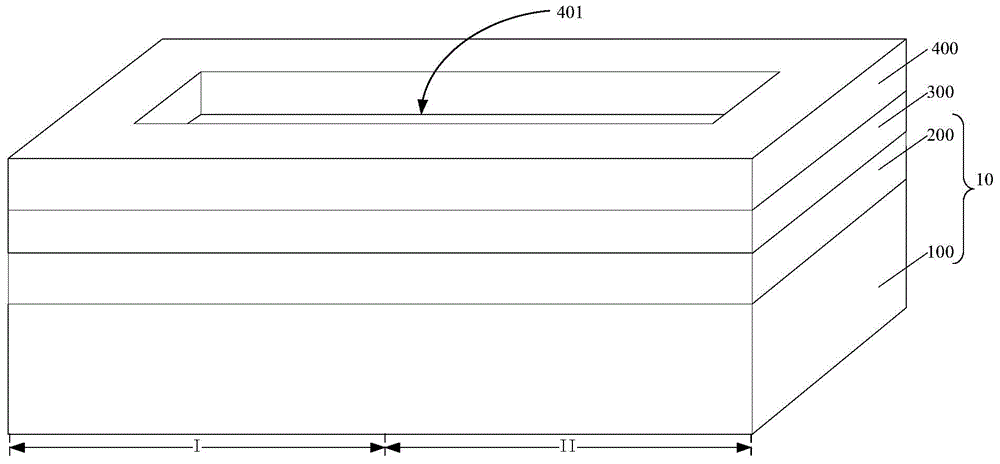

[0036] Please refer to figure 1 , providing a substrate 10 .

[0037] The material of the substrate 10 includes semiconductor materials such as silicon, germanium, silicon germanium, gallium ars...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com