Hardware realizing system for improved LZ4 compression algorithm

A hardware implementation and compression algorithm technology, applied in electrical components, code conversion, etc., can solve the problems of low processing efficiency, large CPU resource occupation, poor compression rate, etc., and achieve the goal of reducing CPU load, strong processing performance, and low delay Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical scheme of the present invention is described in detail below in conjunction with accompanying drawing:

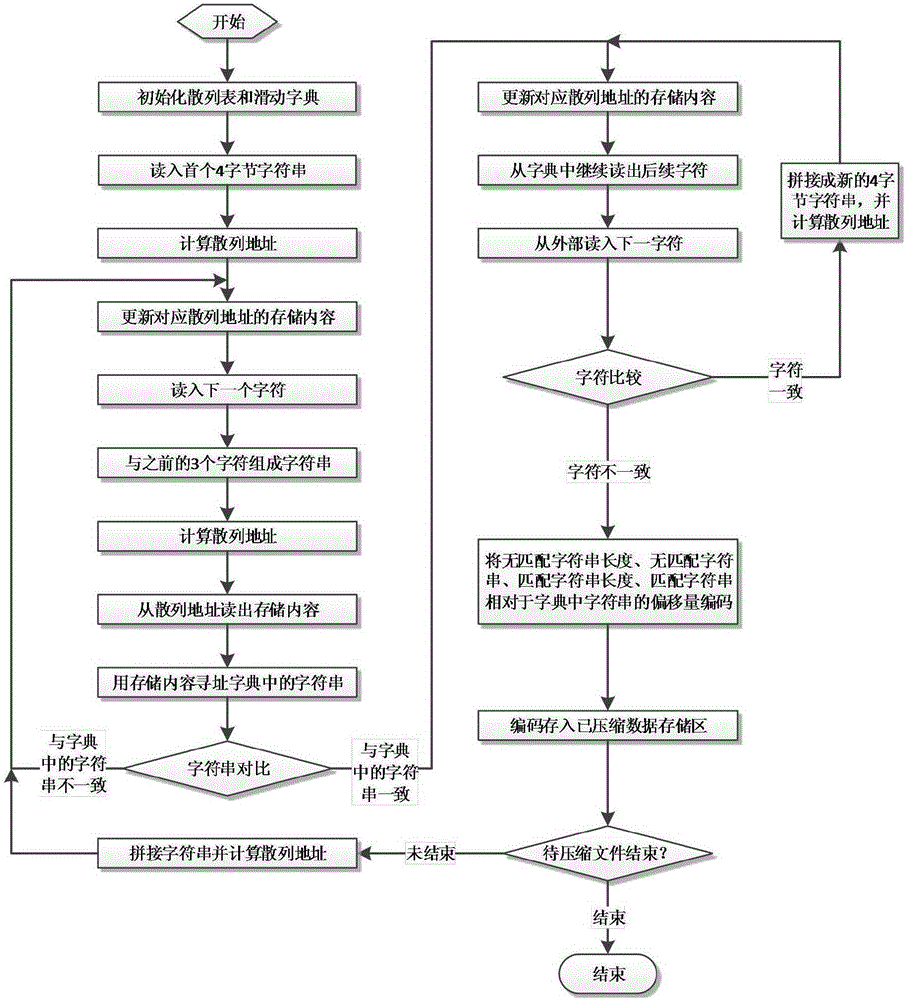

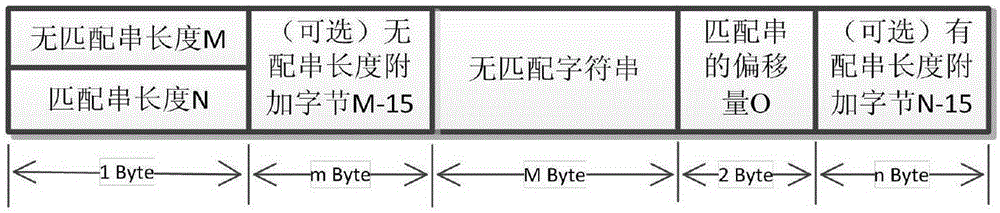

[0035] figure 1 It is a kind of improved LZ4 compression algorithm flowchart of the present invention; As figure 1 Shown, a kind of improved LZ4 compression algorithm of the present invention comprises the following steps:

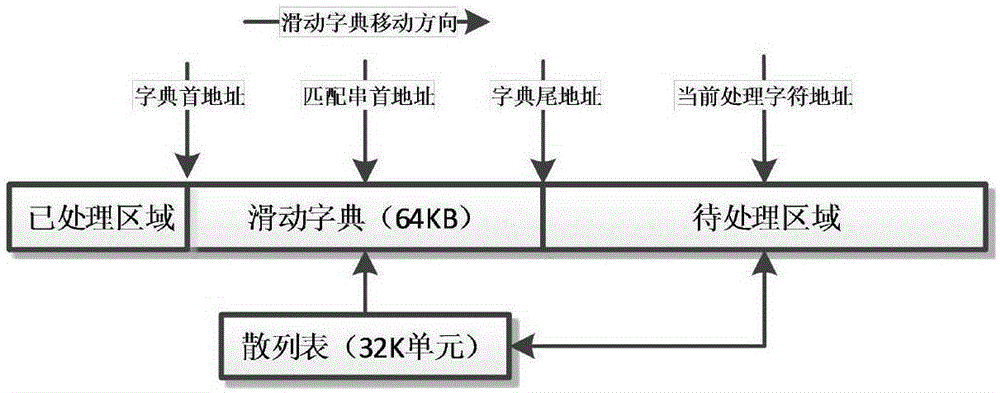

[0036] Step 1. Initialize the hash table and sliding dictionary. The contents of all hash table storage units are initialized to 0. The initial address and tail address of the sliding dictionary coincide, that is, the capacity of the sliding dictionary is 0; when the hardware circuit is initialized, the size of the sliding dictionary is 0. , and then process the subsequent characters one by one, and the processed characters will gradually become part of the sliding dictionary until the continuous characters contained in the sliding dictionary reach 64KB;

[0037]Step 2, read in the first 4-byte character string from the file to be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com