Array substrate, display panel and display device

A technology of array substrates and substrate substrates, applied in static indicators, instruments, etc., can solve the problems of increased power consumption of shift register unit output delay gate drive circuits, increased clock signal delays, increased number of parasitic capacitances, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

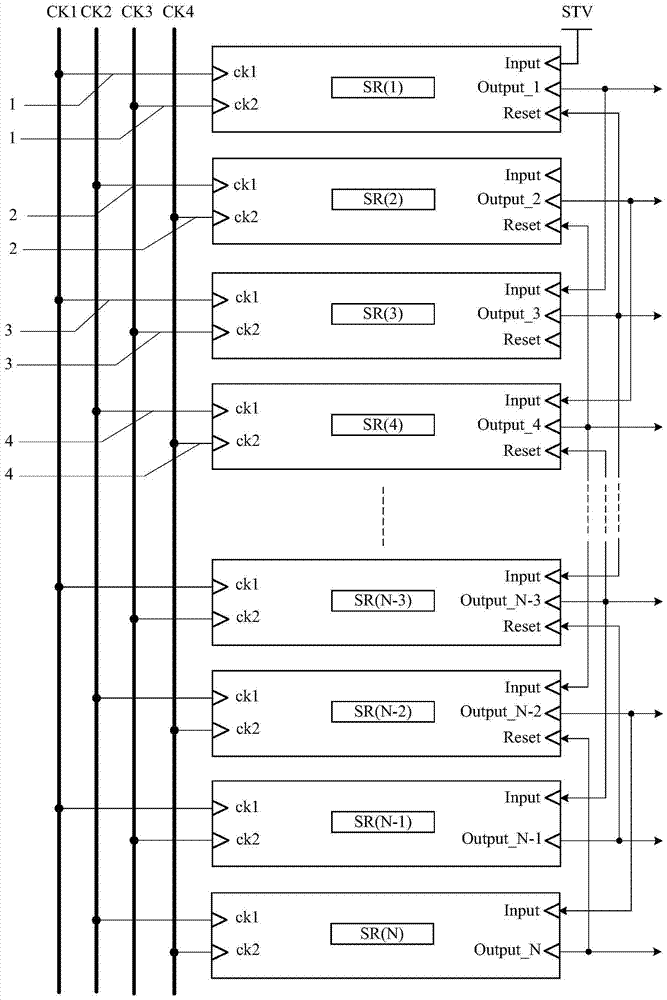

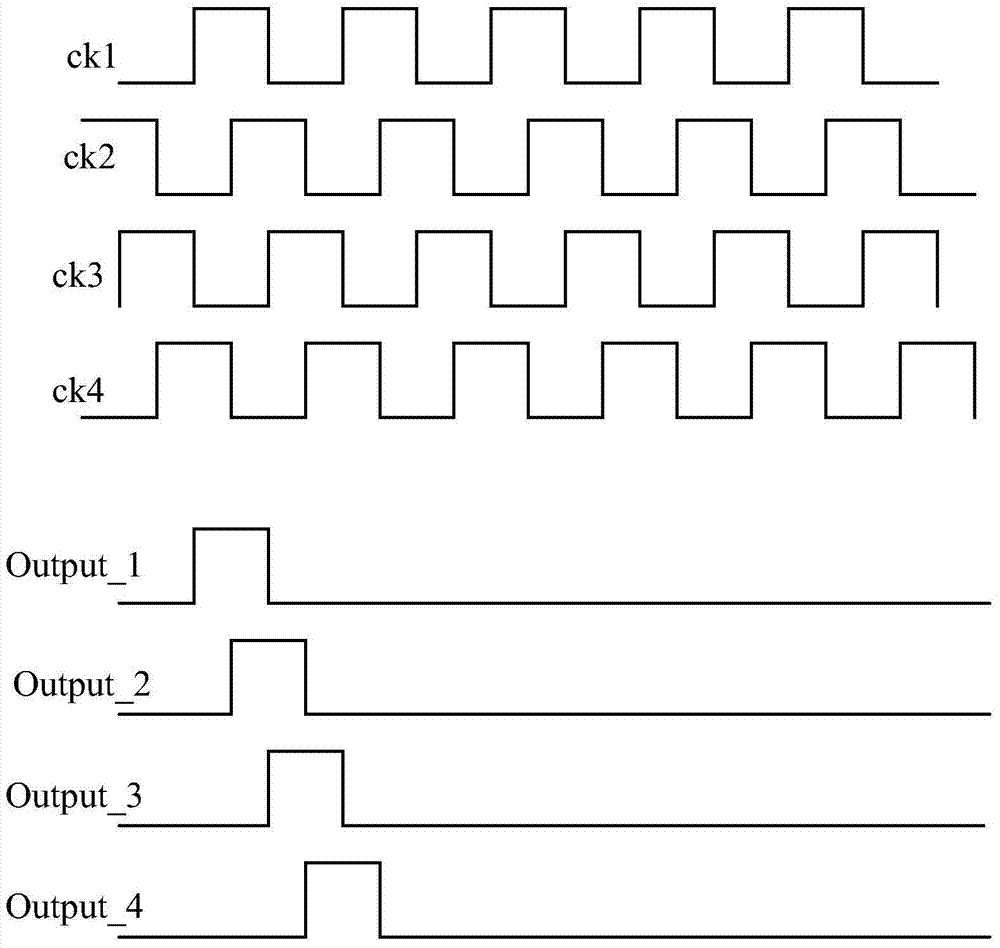

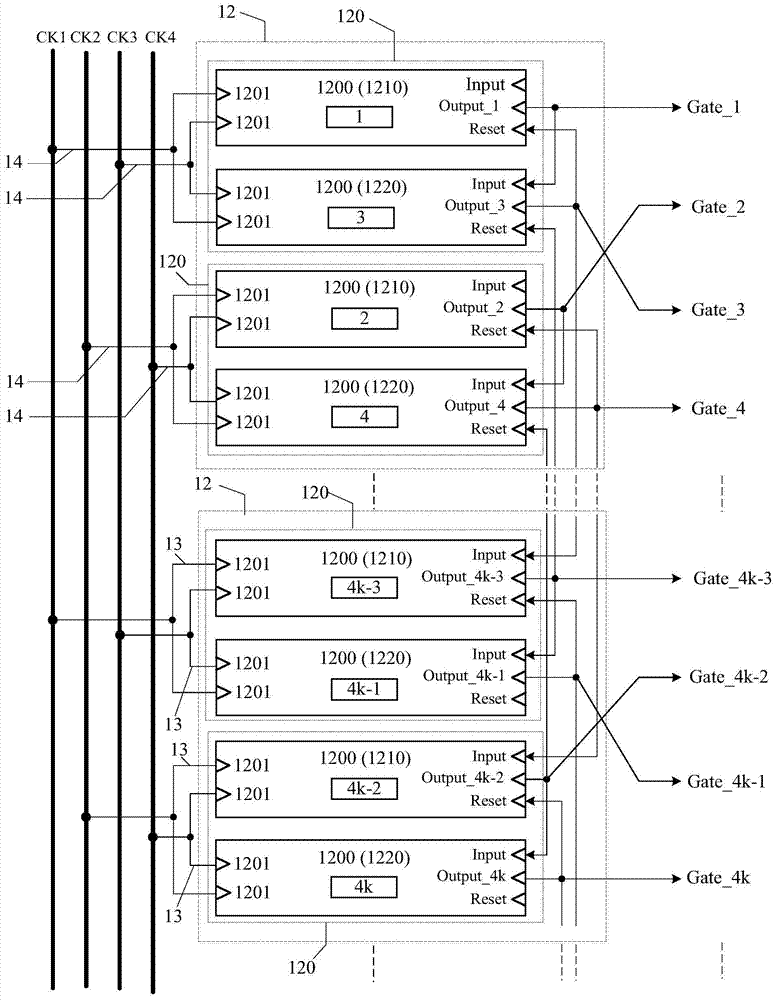

[0074] Take n equal to 2 as an example, such as Figure 3a As shown, it includes a base substrate (not shown in the figure), 2 sets of clock signal lines arranged side by side on the base substrate, and a set of clock signal lines (CK1, CK2, CK3 and CK4) on one side A gate drive circuit with a charging function; wherein the gate drive circuit includes cascaded multi-stage shift register units 1200 arranged side by side along the extension direction of the clock signal line, each of the shift register units has two clock signals The terminals 1201 are respectively used to receive clock signals with opposite phases, and the shift register units 1200 of each level correspond to a group of clock signal lines;

[0075] All the shift register units 1200 are divided into N shift register unit groups 12, for the kth shift register unit group 12, including the 4k-3 shift register unit 1200 to the 4k shift register unit 1200 ; Wherein, the shift register unit 1200 of the 4k-3 level to ...

Embodiment 2

[0084] Take n equal to 3 as an example, such as Figure 3b As shown, it includes a base substrate (not shown in the figure), 3 sets of clock signal lines arranged side by side on the base substrate, and 3 sets of clock signal lines (CK1, CK2, CK3, CK4, CK5 and CK6) A gate drive circuit with a pre-charging function on the side; wherein the gate drive circuit includes cascaded multi-stage shift register units 1200 arranged side by side along the extension direction of the clock signal line, each of which has The two clock signal terminals 1201 are respectively used to receive clock signals with opposite phases, and the shift register units 1200 of each level correspond to a group of clock signal lines;

[0085] All shift register units 1200 are divided into N shift register unit groups 12, for the kth shift register unit group 12, including the 6k-5th stage shift register unit 1200 to the 6kth stage shift register unit 1200 ; Wherein, the shift register unit 1200 of the 6k-5 le...

Embodiment 3

[0094] Take n equal to 2 as an example, such as Figure 3c As shown, it includes a base substrate (not shown in the figure), two sets of clock signal lines arranged side by side on the base substrate, and a gate with a pre-charge function on one side of the two sets of clock signal lines (CK1 and CK2). Pole drive circuit; wherein, the gate drive circuit includes cascaded multi-stage shift register units 1200 arranged side by side along the extension direction of the clock signal line, each of the shift register units has two clock signal terminals 1201 for Receiving clock signals with opposite phases and the shift register units 1200 at each level correspond to a group of clock signal lines;

[0095] For the kth shift register unit group 12, each adjacent two first-type shift register units 1210 and second-type shift register units 1220 are used as a subgroup 120, and two shift register units in each subgroup 120 The bit register unit 1200 corresponds to the same group of clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com