Circuit and method for dynamically generating symmetric cipher with round key

A technology of symmetric cryptography and round key, which is applied in the field of dynamically generating symmetric cryptography by round key, can solve the problems of occupying RAM area and low data throughput rate, and achieve the effect of increasing throughput rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

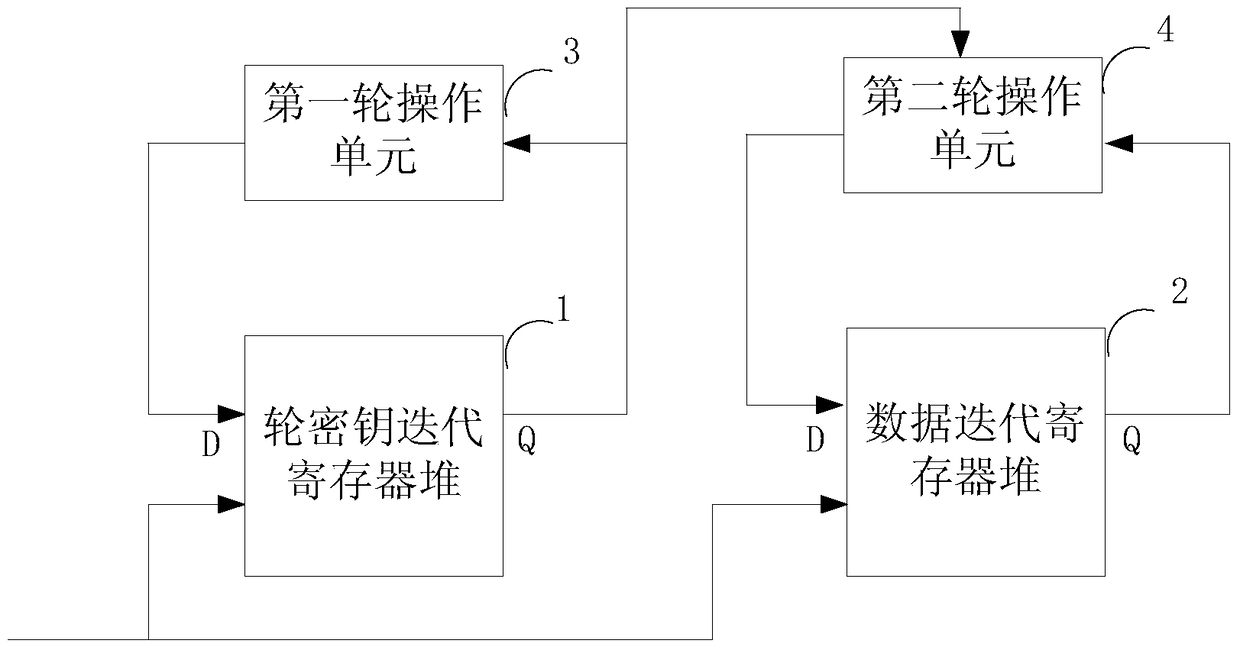

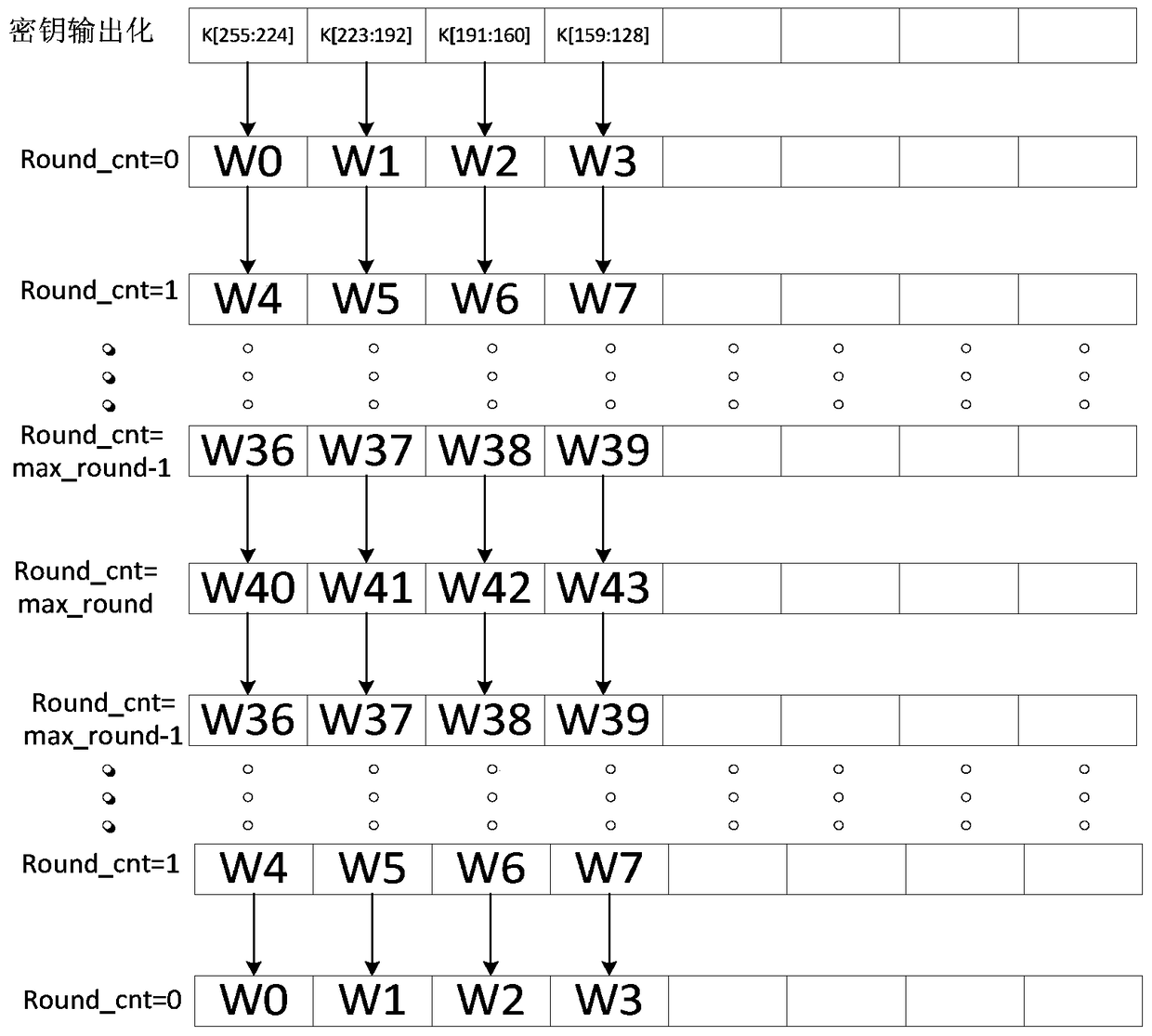

[0028] figure 1 A specific structural block diagram of a circuit for dynamically generating a symmetric cipher by a round key provided in Embodiment 1 of the present invention is shown. For convenience of description, only parts related to the embodiment of the present invention are shown. In this embodiment, the circuit includes: a round key iteration register file 1, a data iteration register file 2, a first round operation unit 3 and a second round operation unit 4, the round key iteration register file 1 and data iteration The register 2 stack is composed of several 32-bit D flip-flops, the output terminal Q of the round key iteration register stack 1 is connected to the input terminal of the first round operation unit 3, and the output terminal of the first round operation unit 3 is connected to the round key iteration The input end of the register file 1; the output end of the data iteration register file 2 and the output end of the round key iteration register file 1 ar...

Embodiment 2

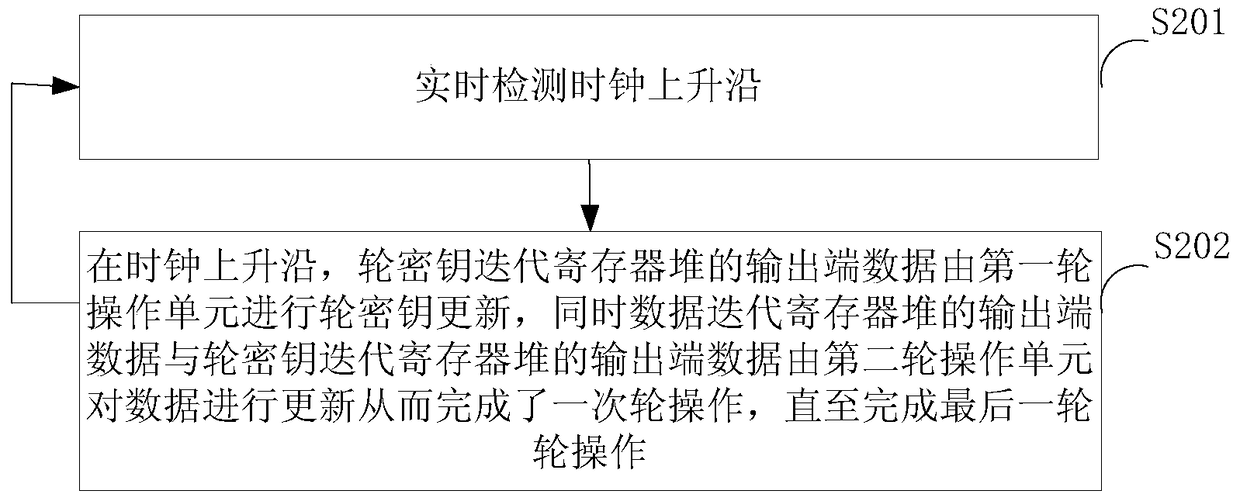

[0033] figure 2 The implementation flow of the method for dynamically generating a symmetric cipher with a round key provided in Embodiment 2 of the present invention is shown, and the details are as follows:

[0034] In step S201, a clock rising edge is detected in real time.

[0035] In this embodiment, CLK is a clock signal. Before the rising edge of the clock arrives, the data of the output terminal Q of the data iteration register file and the data of the output terminal Q of the round key iteration register file are received after passing through the second round operation unit. Input D on the data iteration register file.

[0036] In step S202, at the rising edge of the clock, the data at the output end of the round key iteration register file is updated by the first round operation unit, and at the same time the output end data of the data iteration register file and the output of the round key iteration register file The terminal data is updated by the second-round...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com