HBT (heterojunction bipolar transistor) circuit chip temperature analysis method based on MATLAB (matrix laboratory) programming

An analysis method and circuit chip technology, applied in the field of microelectronics, can solve the problems of inability to analyze large-scale circuit temperature, time-consuming and labor-intensive, affecting circuit reliability, etc., to avoid the meshing process, improve reliability, and avoid power consumption. time consuming effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

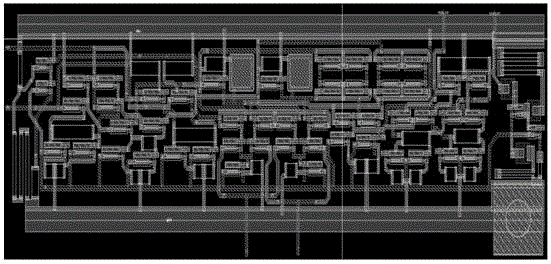

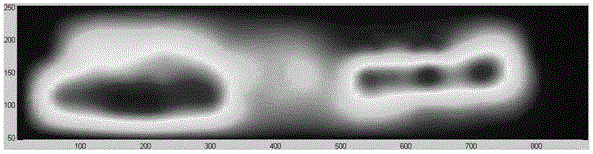

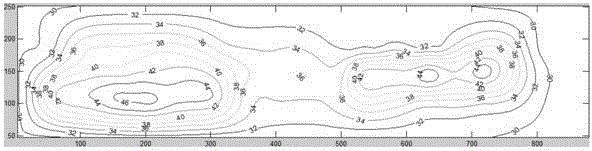

[0023] In order to further illustrate the present invention, below in conjunction with figure 1 process for figure 2 The circuit layout example shown is subjected to temperature analysis. figure 2 The circuit layout shown is the sample-and-hold module layout of the analog-to-digital converter ADC circuit, which uses the InGaP / GaAs HBT process of WIN's H01U-10.

[0024] Step 1, obtaining the geometric dimensions and material thermal conductivity of the heterojunction bipolar transistor (HBT) device used in the circuit.

[0025] According to the used heterojunction bipolar transistor HBT process library file, obtain figure 2 The information of the HBT device in the medium includes the area of the entire device, the area of the base area, the area of the collector area and the materials used, as well as the substrate material, thickness and backside process.

[0026] Step 2, use Comsol finite element analysis software to model the device obtained in step 1.

[0027] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com