High-speed bridge device for AHB (advanced high-performance bus) accessing on-chip SRAM (static random access memory) and operating method of high-speed bridge device

A working method and bus technology, applied in the direction of memory address/allocation/relocation, instrument, electrical digital data processing, etc., can solve the problem of efficiency reduction and achieve the effect of avoiding the reduction of system continuous reading efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described below in conjunction with the accompanying drawings.

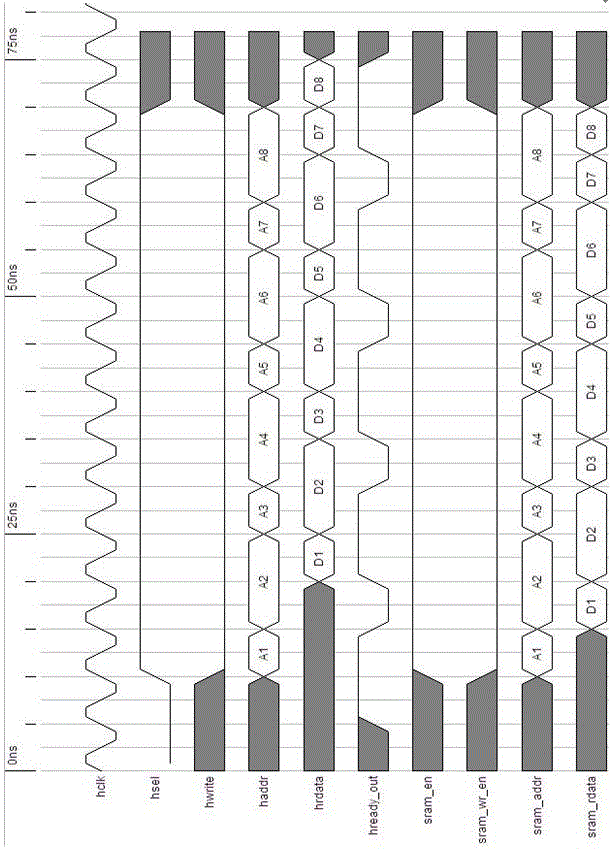

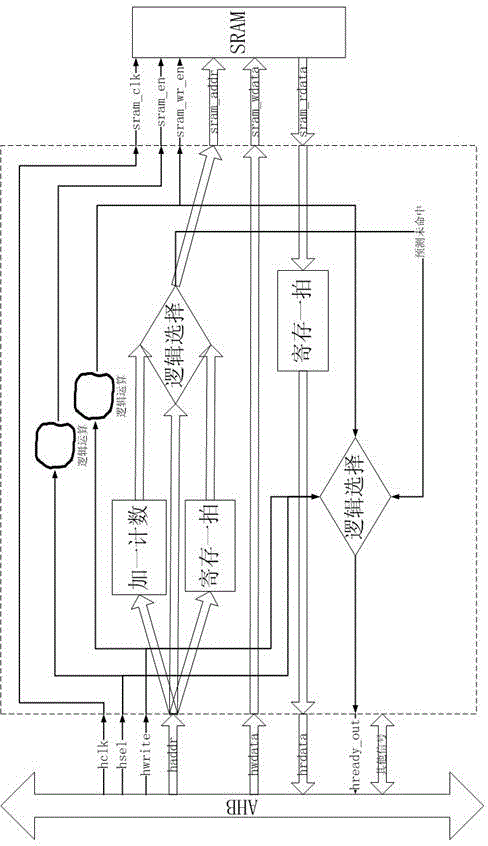

[0026] like image 3 As shown, the present invention adds an address prediction mechanism on the basis of the ordinary AHB to SRAM bridge, compares the bus address and the predicted address, and if they are consistent, the reading can be read in the SRAM one clock cycle in advance, ensuring that the chip meets the timing requirements and the data can be continuous Transmission; the predicted address refers to the address obtained by adding one count. Suppose the address on the current bus is 0x0000_1234. It is the predicted address, and the predicted address is used as the SRAM address when the data of the read operation is returned. Therefore the cost of the present invention is only to increase a 1-up counter and related control logic on the basis of the common bridge, and will not exceed several hundred gates, and the efficiency can be increased by one-third when t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com