Off-core cache device

A high-speed cache and cache technology, applied in memory systems, memory address/allocation/relocation, instruments, etc., can solve the problems of difficult integration, inflexibility, and non-volatile memory access characteristics design, etc., to reduce Access delay, high flexibility, and improved memory access performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with the accompanying drawings.

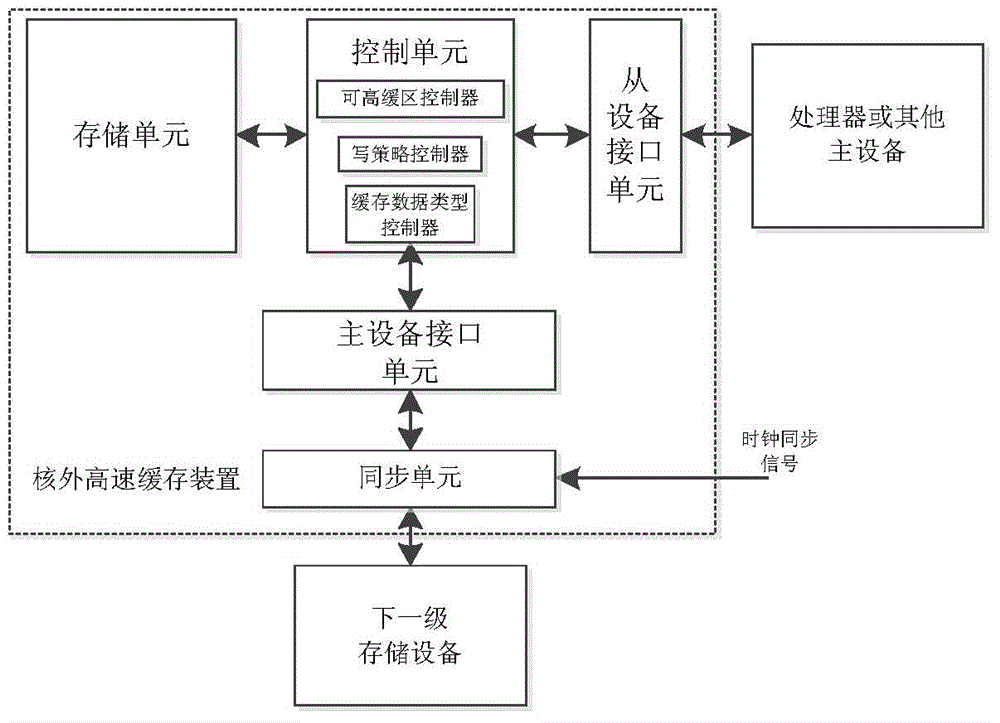

[0027] refer to Figure 1 to Figure 6 , an out-of-core cache device used in a SoC system chip, comprising:

[0028] The slave device interface unit receives read and write access requests from the processor or other master devices, and sends the access requests to the control unit; receives cached data or response information returned by the control unit, and sends them to the processor or other master devices.

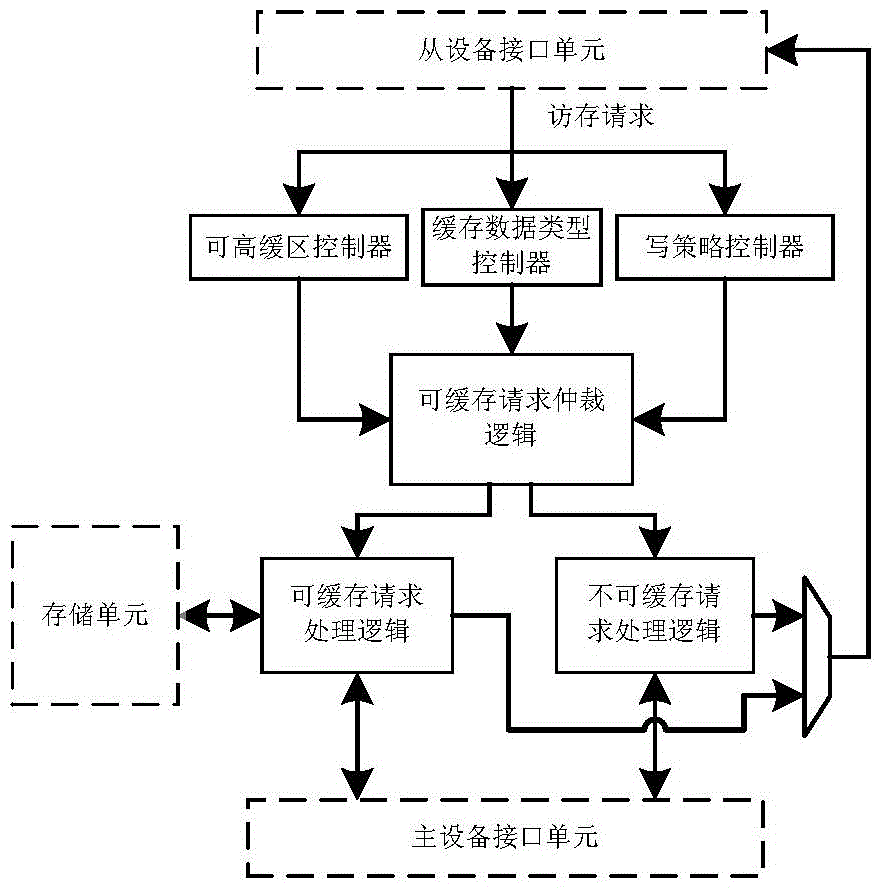

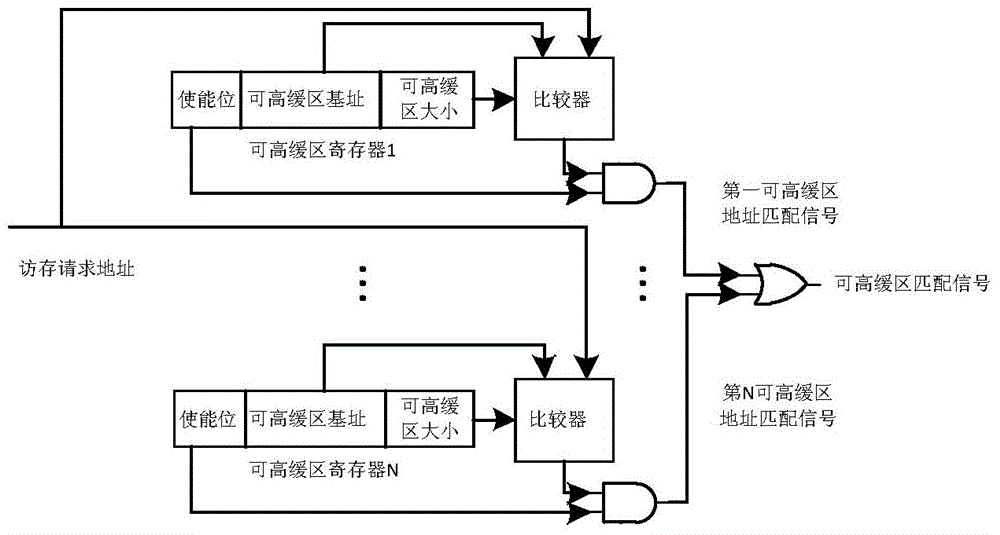

[0029] The control unit includes a cacheable area controller, a write strategy controller and a cache data type controller, receives the cache read and write access request sent by the slave device interface unit, and accesses the storage unit or directly sends the request according to the register configuration information to the master device interface unit, and then return the obtained cached data or response information to the slave device interface unit....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com