A Pipeline Commitment Method for Store Instructions in a Superscalar Microprocessor

A technology for storage instructions and microprocessors, which is applied in the field of pipeline submission of storage instructions in superscalar microprocessors. It can solve the problems of slow submission speed and submission of Store instructions, improve utilization rate, improve processor performance, and improve processing The effect of device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Below in conjunction with specific embodiment, further illustrate the present invention. It should be understood that these examples are only used to illustrate the present invention and are not intended to limit the scope of the present invention. In addition, it should be understood that after reading the teachings of the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

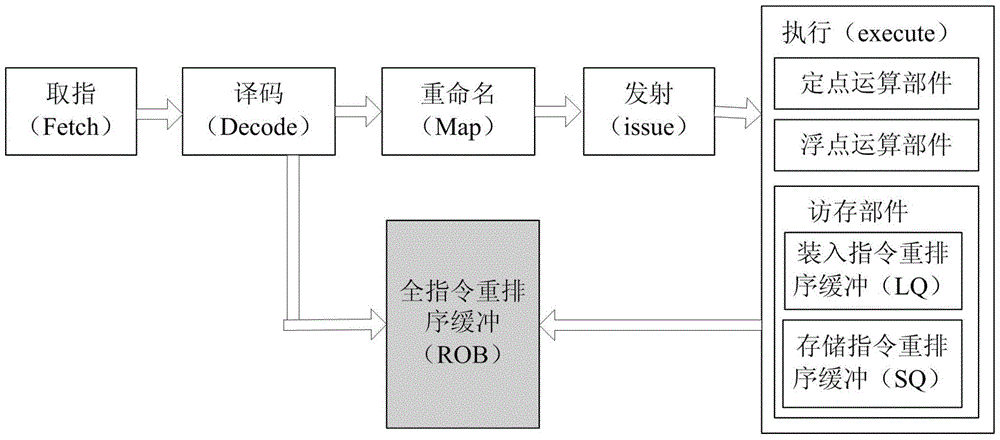

[0041] Embodiments of the present invention relate to a method for implementing storage instruction pipeline submission in a superscalar microprocessor, such as figure 2 shown, including the following steps:

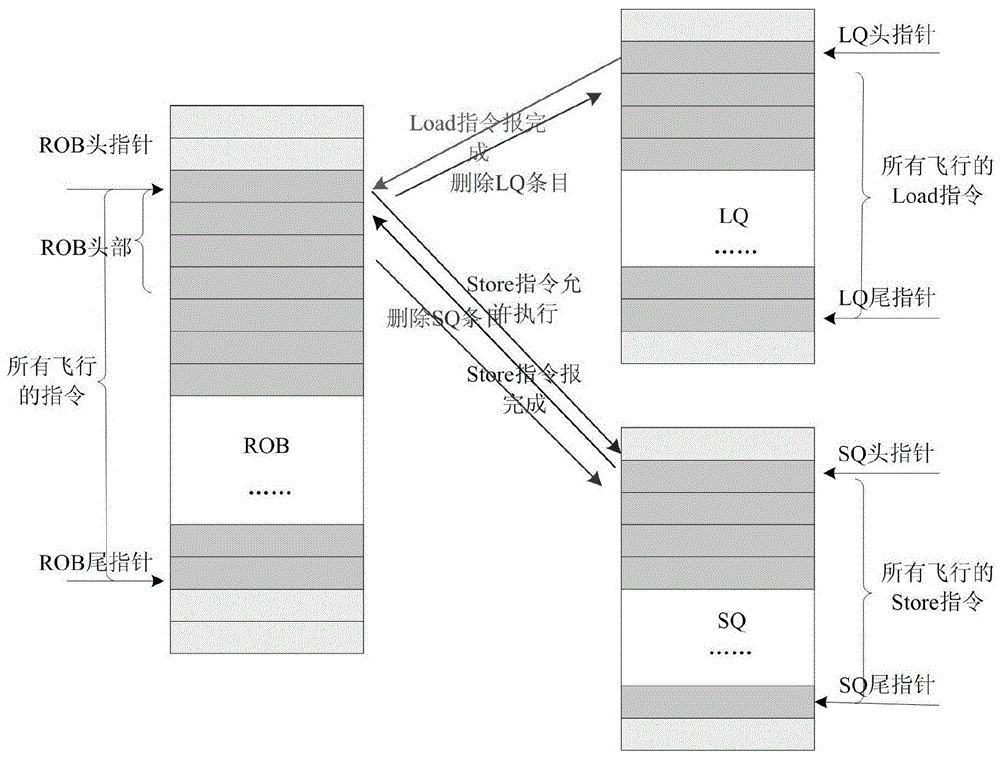

[0042] (1) The full instruction reordering buffer starts from the current head pointer, checks the status of n instructions at the head, selects the age sequence number of the youngest instruction that is currently allo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com