Optimization method of microprocessor microarchitecture parameters based on petri net

A system structure, microprocessor technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of slow simulation speed, low prediction reliability and accuracy, and inability to configure multiple parameters Simulation and other issues to achieve the effect of rapid modeling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

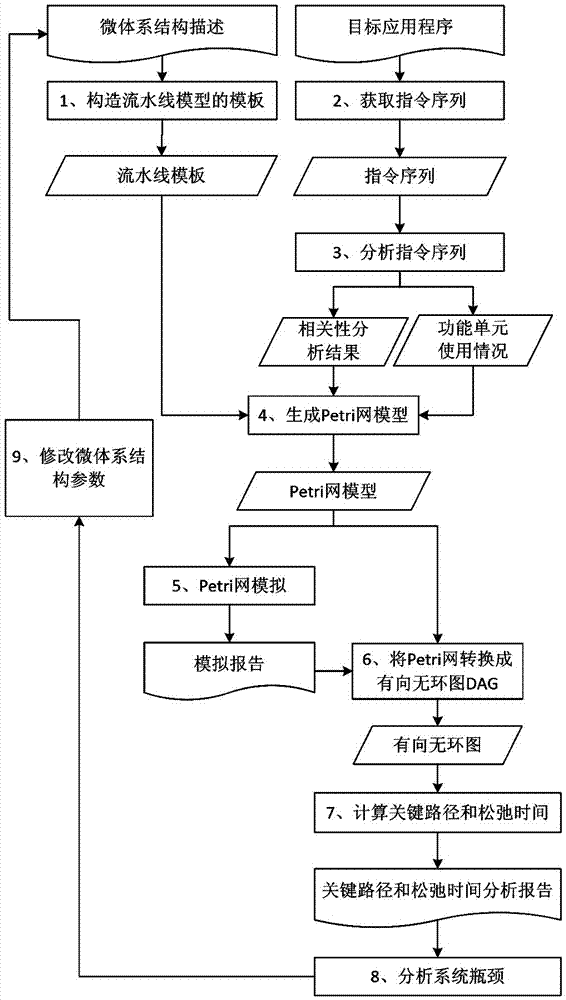

[0071] Such as figure 1 As shown, the implementation steps of the microprocessor microarchitecture parameter optimization method based on Petri net in this embodiment are as follows:

[0072] 1) According to the microarchitecture of the microprocessor, the template of the pipeline model is constructed based on the colored Petri net.

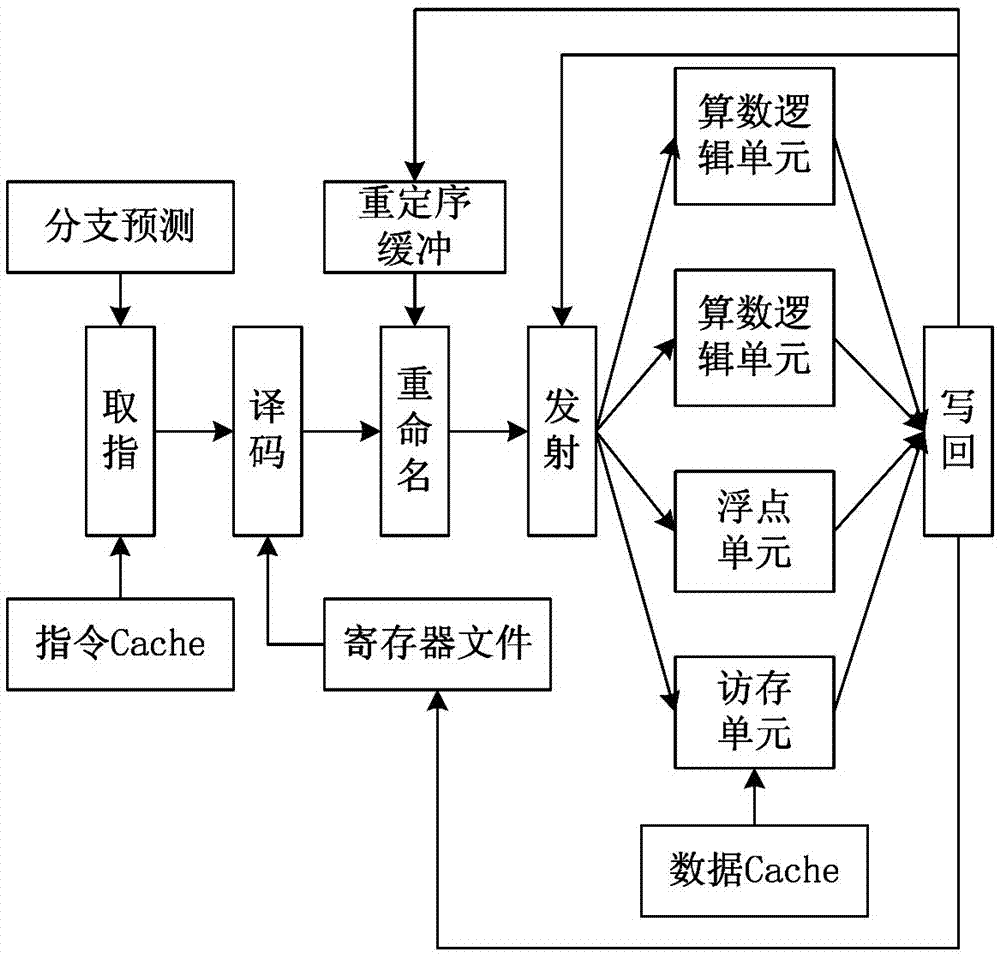

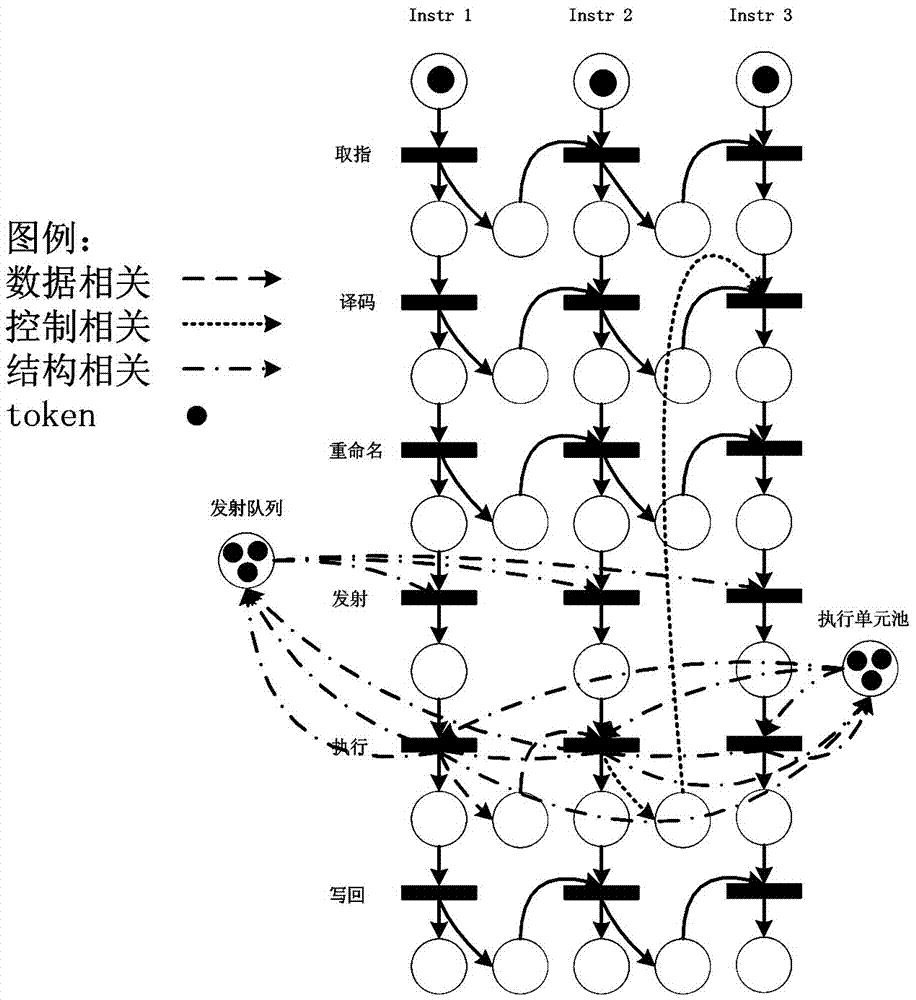

[0073] Such as figure 2 In the abstract diagram of the superscalar pipeline shown, the pipeline includes 6 pipeline segments, which are fetch, decode, rename, issue, execute (exe) and write Back (commit), where the execution (exe) includes 2 arithmetic logic units (ALU), 1 floating point unit (FP), and 1 memory access unit (load / store). The pipeline model is to describe the structure of such a pipeline. The template of the pipeline model describes the structure of the pipeline, the number of various resources in the pipeline, resource competition and arbitration, etc. In this embodiment, the storage space, the quantity and type of various res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com