Vertical-cavity surface-emitting semiconductor laser

A vertical cavity surface emission and semiconductor technology, applied in the field of lasers, can solve the problems of low output power and poor stability of VCSEL, and achieve the effects of high power and high stability single-mode output, increased loss, and increased gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0031] The preparation method of the above-mentioned vertical cavity surface emitting semiconductor laser comprises the following steps:

[0032] Step 1. Cleaning the epitaxial wafer, performing photolithography and development on the p-side of the cleaned epitaxial wafer for the first time, and dry-etching the p-side to appear the P-type DBR mesa 4, and the etching depth just reaches the top of the active region 8;

[0033] Wherein, the epitaxial wafer can be obtained by means known to those skilled in the art, and generally adopts commercial purchase;

[0034] Step 2: Perform oxidation measurement on the P-type DBR mesa 4 to obtain an oxidation-limited layer 6 with oxidation holes 7;

[0035] Step 3, thinning and polishing the substrate 9, and then growing an N-face electrode 10 on the surface of the substrate 9;

[0036]Step 4: On the upper surface of the P-type DBR4, grow a transparent insulating dielectric material with an optical thickness that is an odd multiple of a q...

Embodiment 1

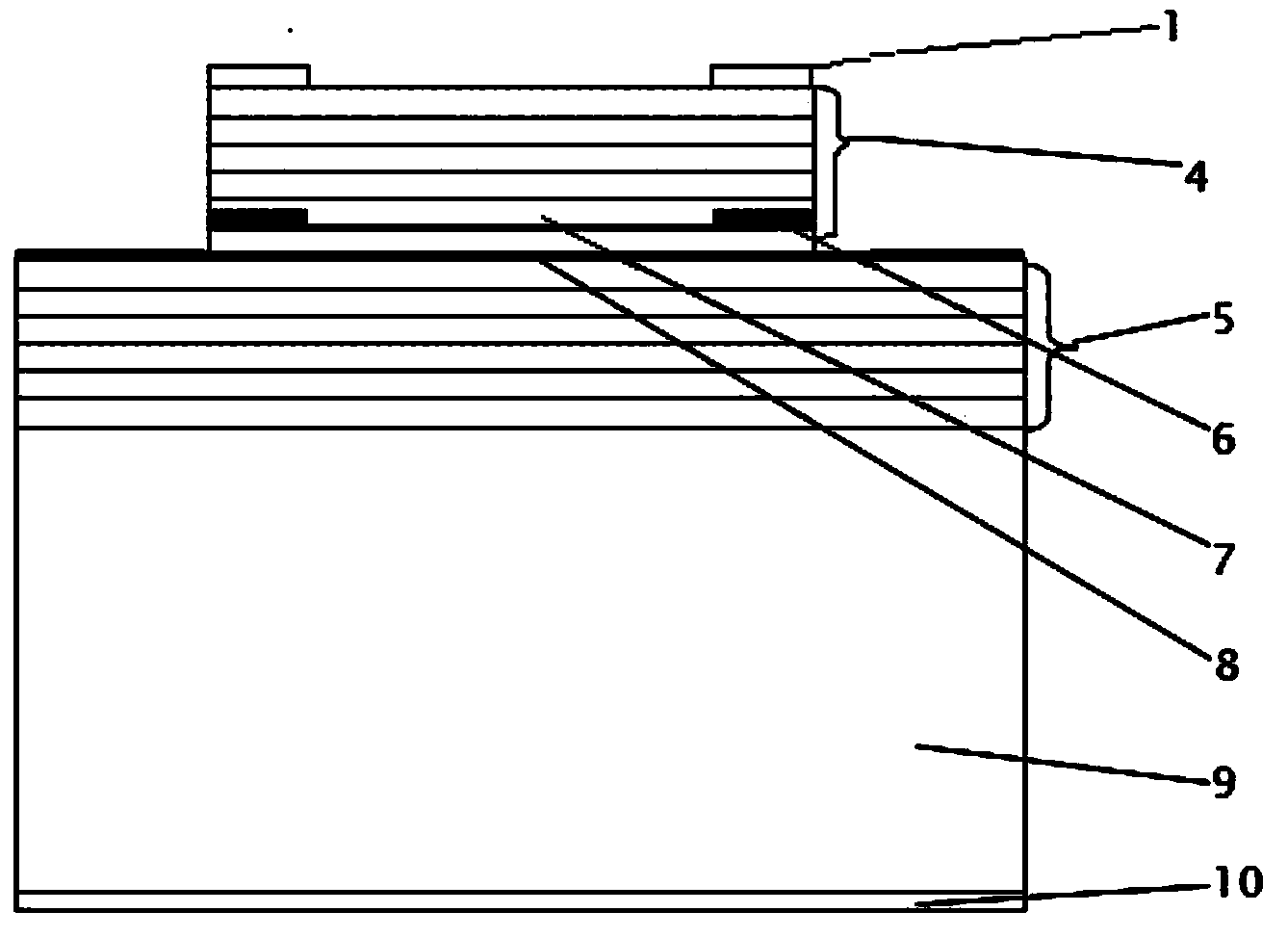

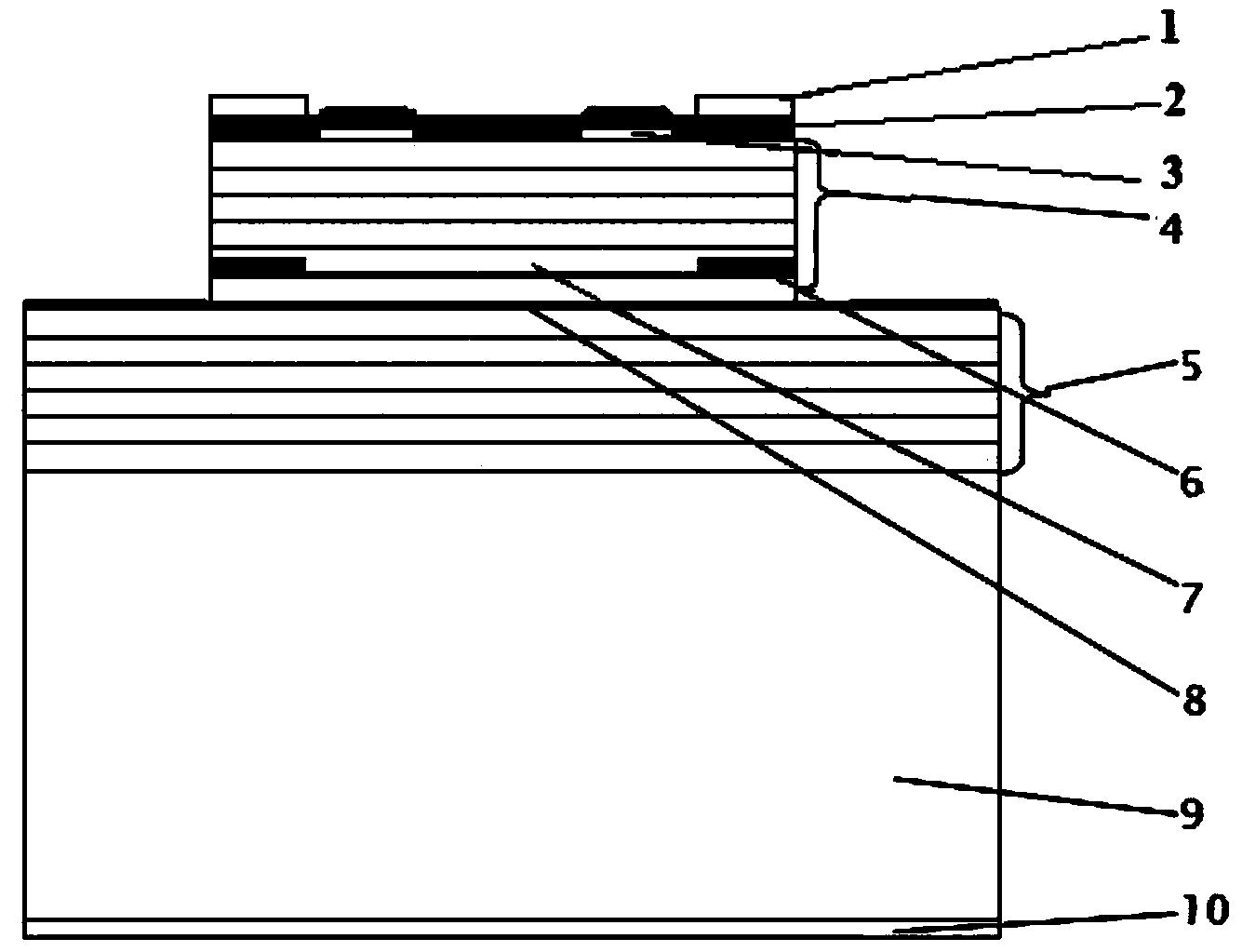

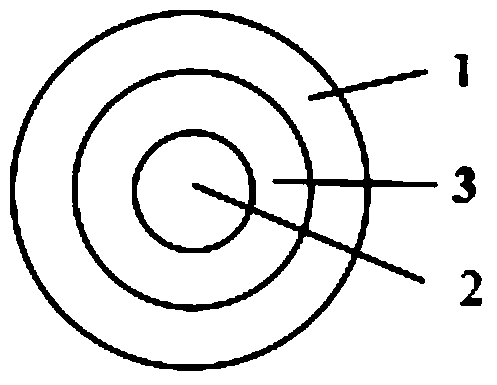

[0040] Such as figure 2 As shown, the vertical cavity surface emitting semiconductor laser includes a P-type DBR4, an active region 8, an N-type DBR5, a substrate 9 and an N-surface electrode 10 arranged in sequence from top to bottom, and a circular oxidation hole is arranged in the P-type DBR4 The oxidation limiting layer 6 of 7 also includes a P-face electrode 1, a transparent conductive film 2 and an annular insulating dielectric film 3, the lower surface of the annular insulating dielectric film 2 is fixed on the upper surface of the P-type DBR4, and blocks the edge of the light exit hole, transparent The conductive thin film 3 is fixed on the upper surface of the annular insulating dielectric film 3 and the exposed P-type DBR4, and blocks the light exit hole, and the P-surface electrode 1 is fixed on the edge of the upper surface of the transparent conductive thin film 3 . The P surface electrode 1 and the annular insulating dielectric film 2 are all in a ring structure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com