Asynchronous fault-tolerant network-on-chip router design method

An on-chip network and design method technology, applied in data exchange networks, instruments, computing, etc., can solve the problems of low average delay and poor routing ability, and achieve the effects of reducing area overhead, good scalability and fault tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] A method for designing an asynchronous fault-tolerant network-on-chip router, the steps of which are as follows:

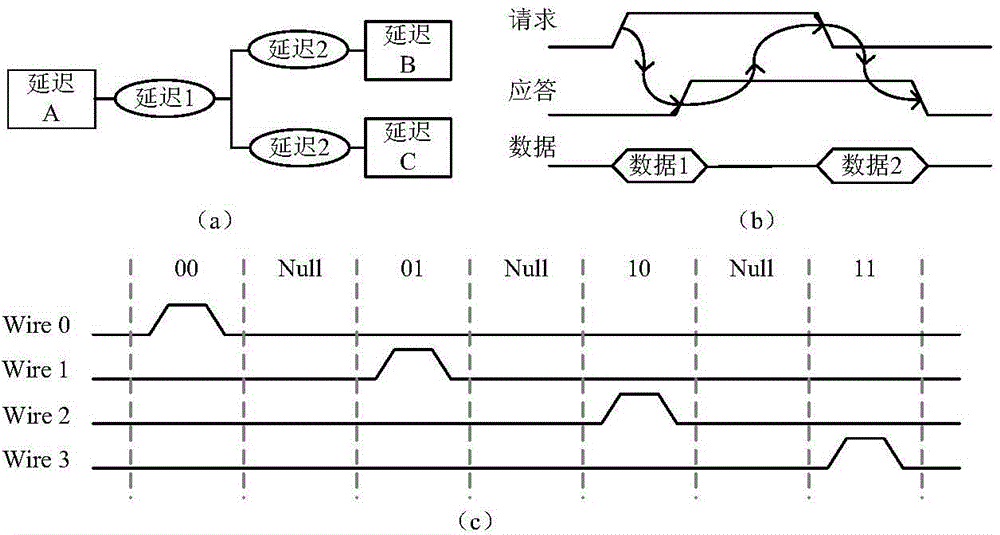

[0037] a. According to the performance to be realized, select the basic mode of asynchronous network-on-chip, such as delay model, handshake protocol, and encoding method, and make a good choice of infrastructure in the early stage.

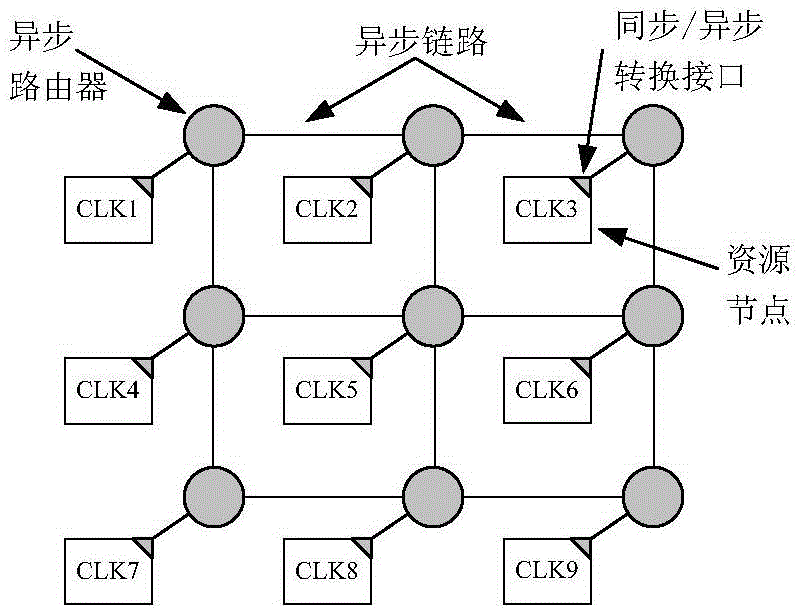

[0038] b. Set the asynchronous network-on-chip data transmission format, first send the data packet to the network through the resource node, and then transmit the data packet to the local resource node of the destination node after reaching the destination.

[0039] c. The asynchronous network-on-chip router architecture is a key component in the asynchronous network-on-chip, which sets the basic components of the router, such as input and output units, and connections between input and output units.

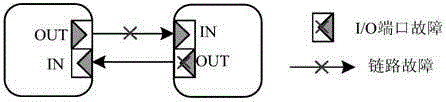

[0040] d. Design an asynchronous network-on-chip fault model. Knowing the fault model, design a routing algorithm for fault tol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com