Preparation method for gate oxide

A gate oxide layer and oxidation process technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problem that the thermal oxidation process cannot improve the interface state in a timely and effective manner, and reduce the possibility of generating interface states. , the effect of stabilizing nitrogen content, improving life and performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that the drawings are all in very simplified form and use imprecise ratios, which are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

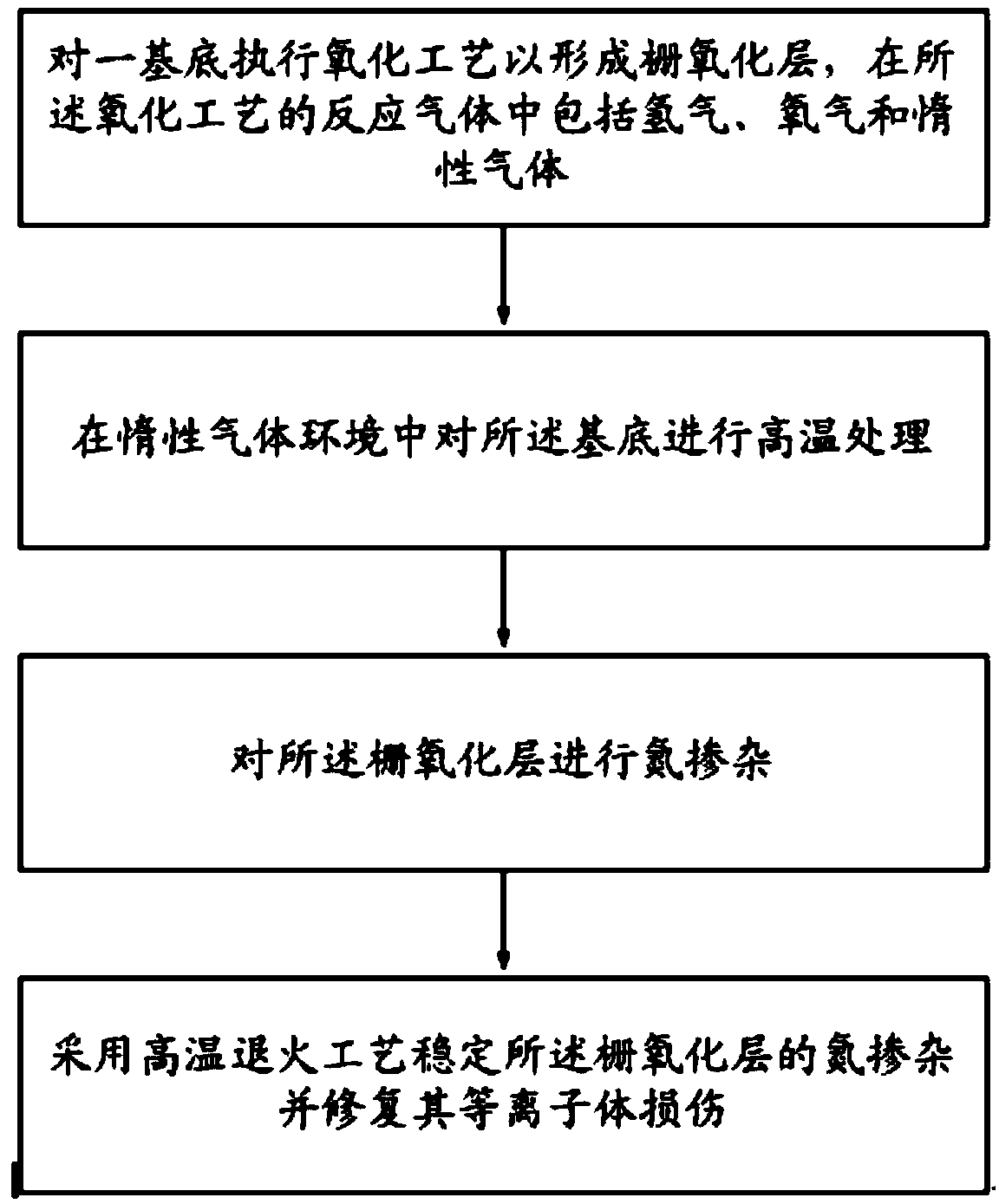

[0023] Such as figure 1 As shown, the preparation method of the gate oxide layer provided by the present invention comprises the following steps:

[0024] S1: performing an oxidation process on a substrate to form a gate oxide layer, wherein a reaction gas in the oxidation process includes an inert gas.

[0025] Among them, the oxidation process described is in-situ water vapor generation (ISSG). ISSG is a new low-pressure rapid oxidation thermal annealing technology, which is currently mainly used in the growth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com