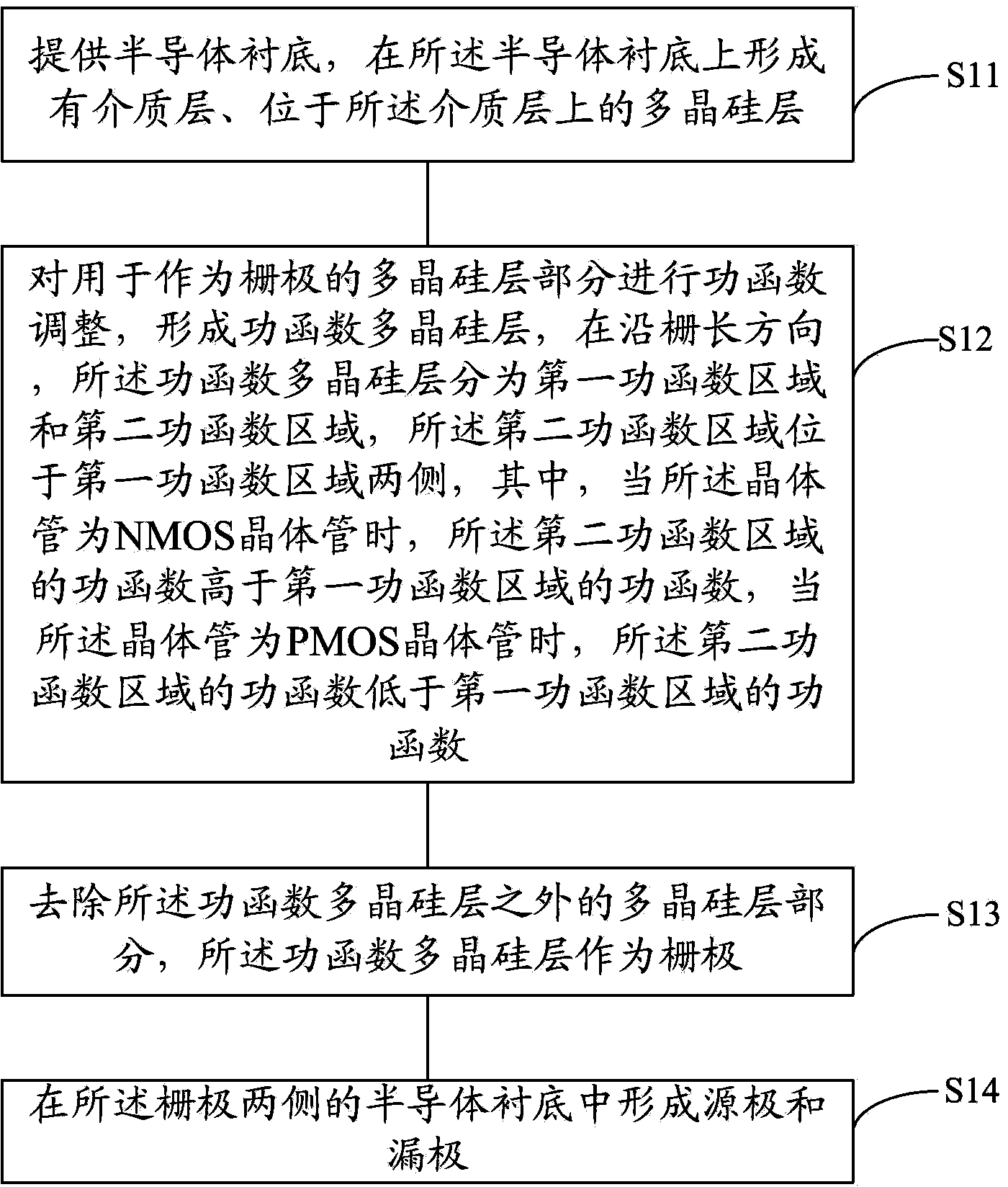

Forming method of transistor

A transistor and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem that the performance of semiconductor devices has not been significantly improved, and achieve the effect of eliminating short-channel effects, uniform distribution, and good performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The following describes the technical solutions of the present invention clearly and completely through specific embodiments in conjunction with the accompanying drawings. Obviously, the described embodiments are only a part of the implementation manners of the present invention, rather than all of them. According to these embodiments, all other implementation manners that can be obtained by a person of ordinary skill in the art without creative labor fall within the protection scope of the present invention.

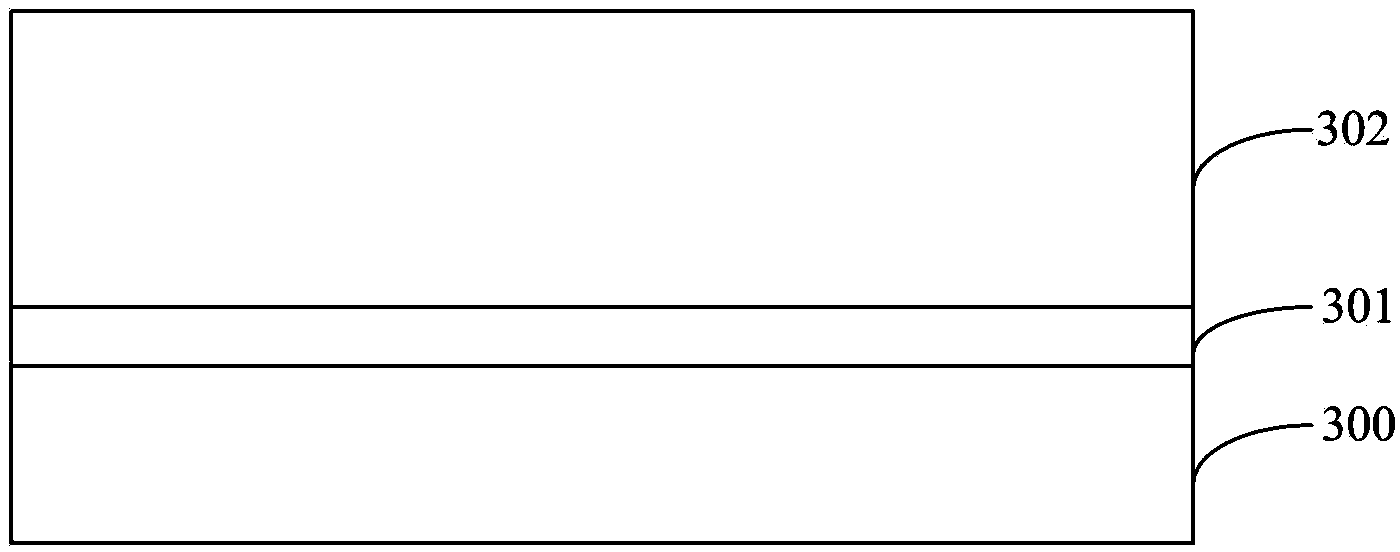

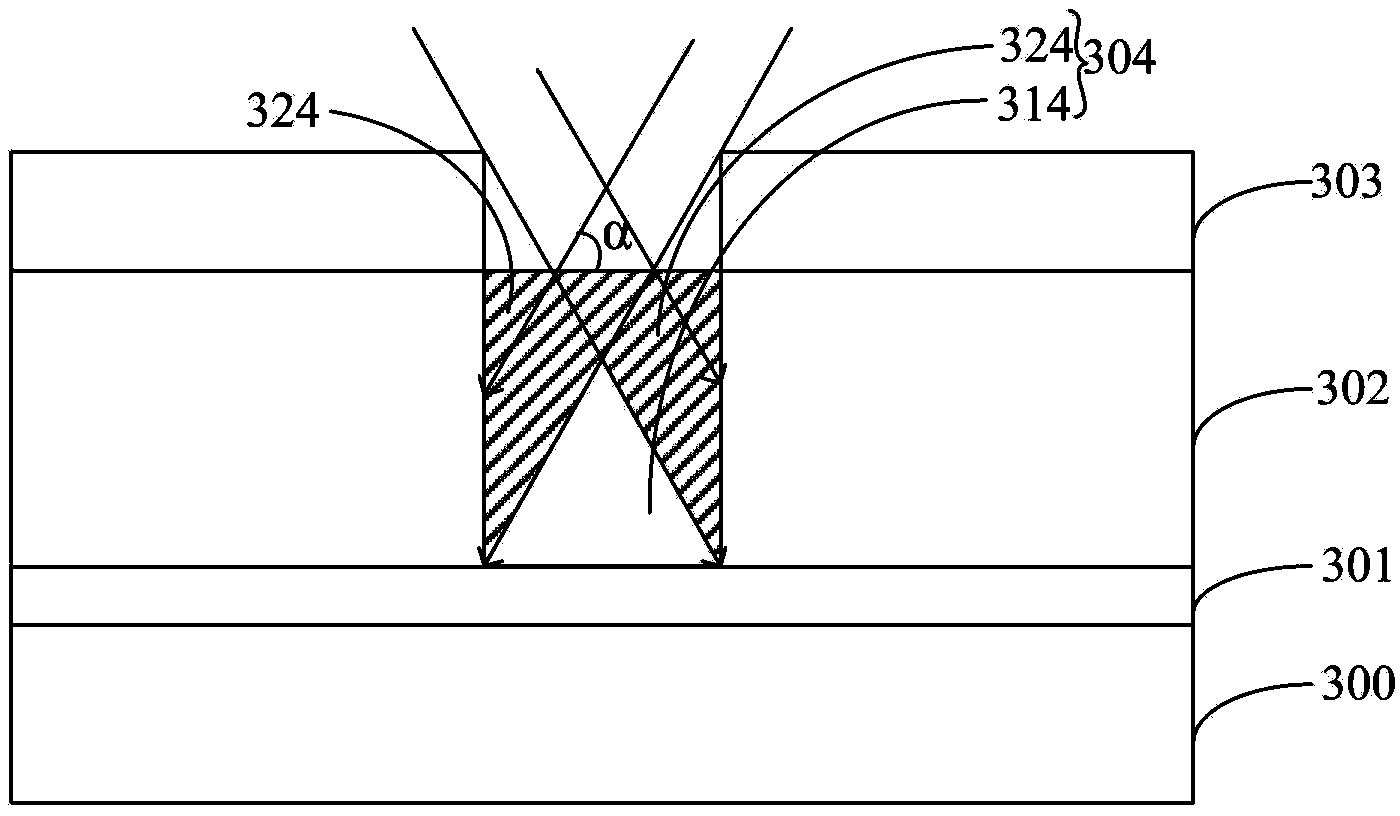

[0036] Refer to figure 2 , Combined with reference figure 1 Step S11 is performed to provide a semiconductor substrate 300, on which a dielectric layer 301 and a polysilicon layer 302 located on the dielectric layer 301 are formed.

[0037] In a specific embodiment, the material of the semiconductor substrate 300 may be single crystal silicon, single crystal germanium or single crystal silicon germanium; it may also be silicon-on-insulator (SOI); or may also include o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com