FPGA testing device and method

A test configuration and self-test technology, which is applied in the field of FPGA test devices, can solve the problems of optimization effect influence, test cost increase, test efficiency impact, etc., to achieve the effect of improving test efficiency, reducing the number of times, and reducing test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0024] The device and method for testing FPGA of the present invention convert the test configuration in the FPGA configuration memory into another group of effective test configurations by utilizing the feedback and superposition device in the data generator and the address generator, so as to reduce the serial number from the outside of the chip. The number of times to load test configurations can be increased to improve test efficiency and reduce test costs.

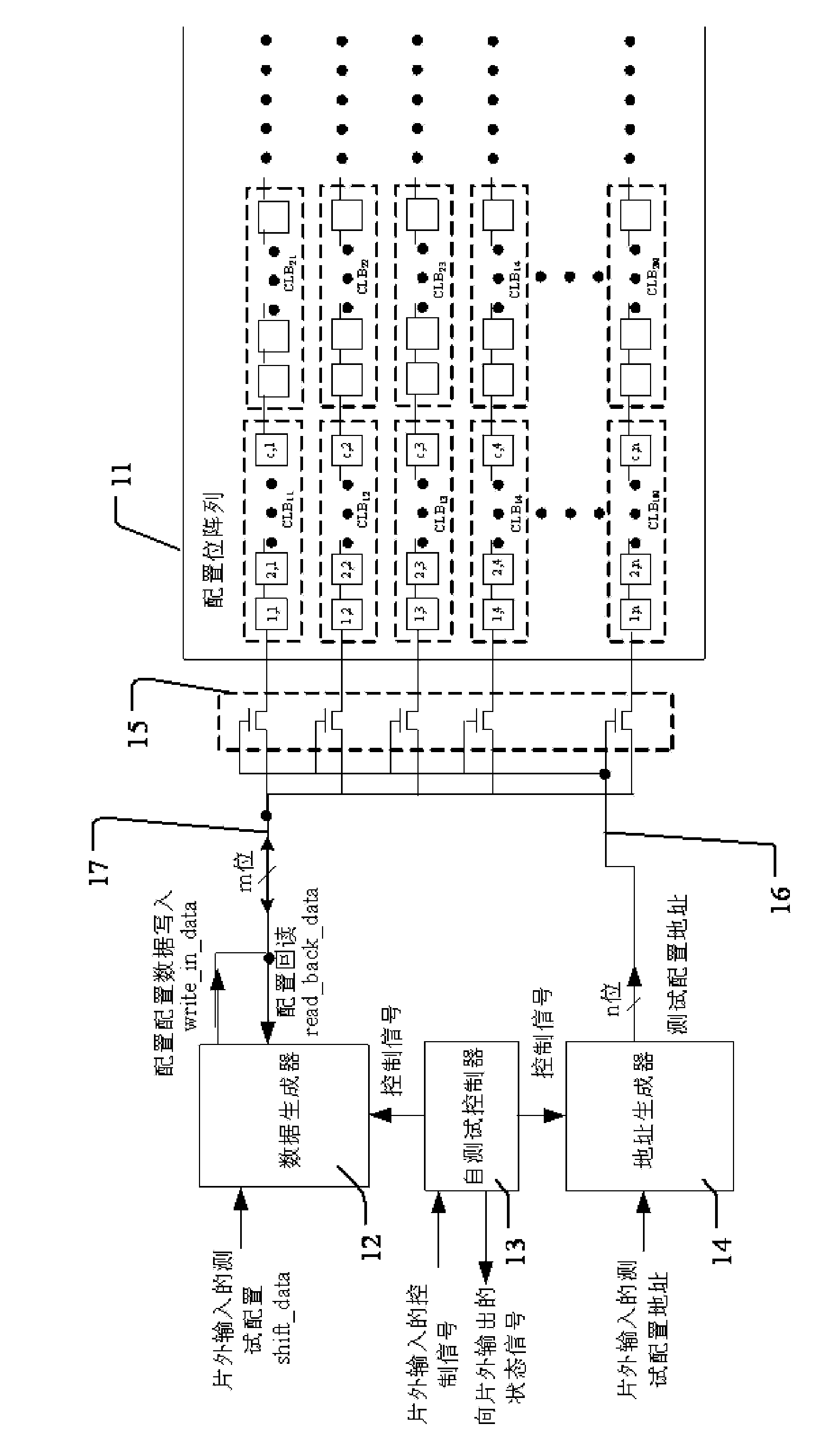

[0025] In an exemplary embodiment of the present invention, a device for testing FPGA is provided. Such as figure 1 As shown, the device for testing FPGA includes: a data generator 12 , an address generator 14 and a self-test controller 13 . Wherein, the self-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com