On-chip network communication deadlock avoidance method, router and communication network

An on-chip communication and network deadlock technology, applied in the field of network communication, to achieve the effect of reducing the probability of multicast deadlock

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Hereinafter, the present invention will be further described in detail through specific embodiments in conjunction with the drawings.

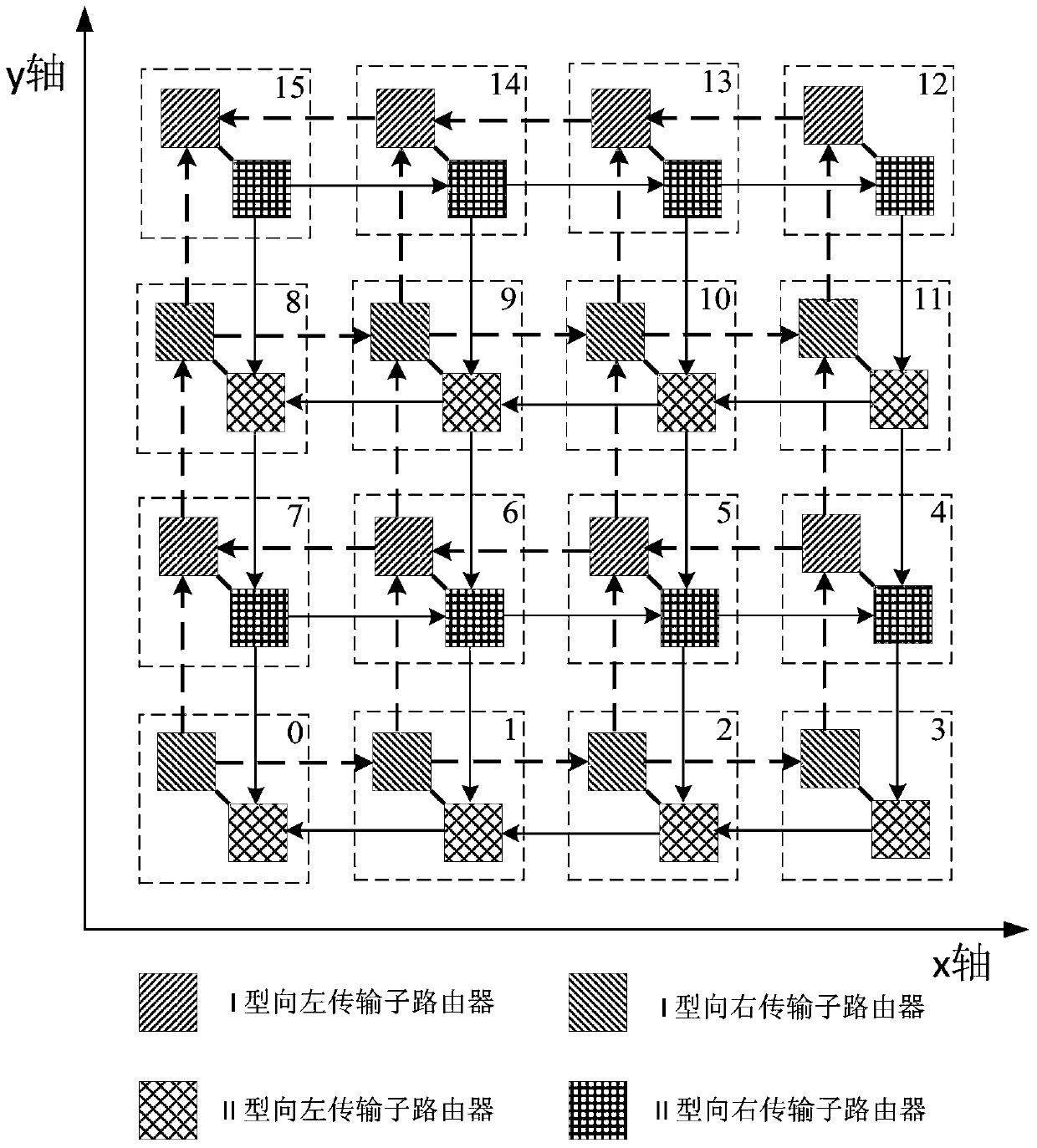

[0028] This embodiment uses a 4*4 network topology, please refer to figure 1 . In other embodiments, as long as the network topology of N*M is adopted, where N and M are both positive integers, and there is no size limit between N and M, they can be the same or different, such as 3*8, 7* 5, 11*1, etc. Multicast communication in the network adopts a tree-based approach and uses wormhole switching. Multicast packets are distinguished in the form of labels. The labeling rules are: the router in the lower left corner of the network is the origin, the horizontal to the right is the positive direction of the x-axis, and the vertical upward is the positive direction of the y-axis; the router is based on its communication network Use a unique natural number label for the difference in the middle position, preferably a unique and continuous natur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com