Ramp generator circuit, and image sensor and image capture device comprising same

A ramp signal and generating circuit technology, applied in signal transmission system, electrical signal transmission system, image communication, etc., can solve problems such as clock waveform passivation, duty cycle degradation, differential nonlinear) characteristic degradation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach >

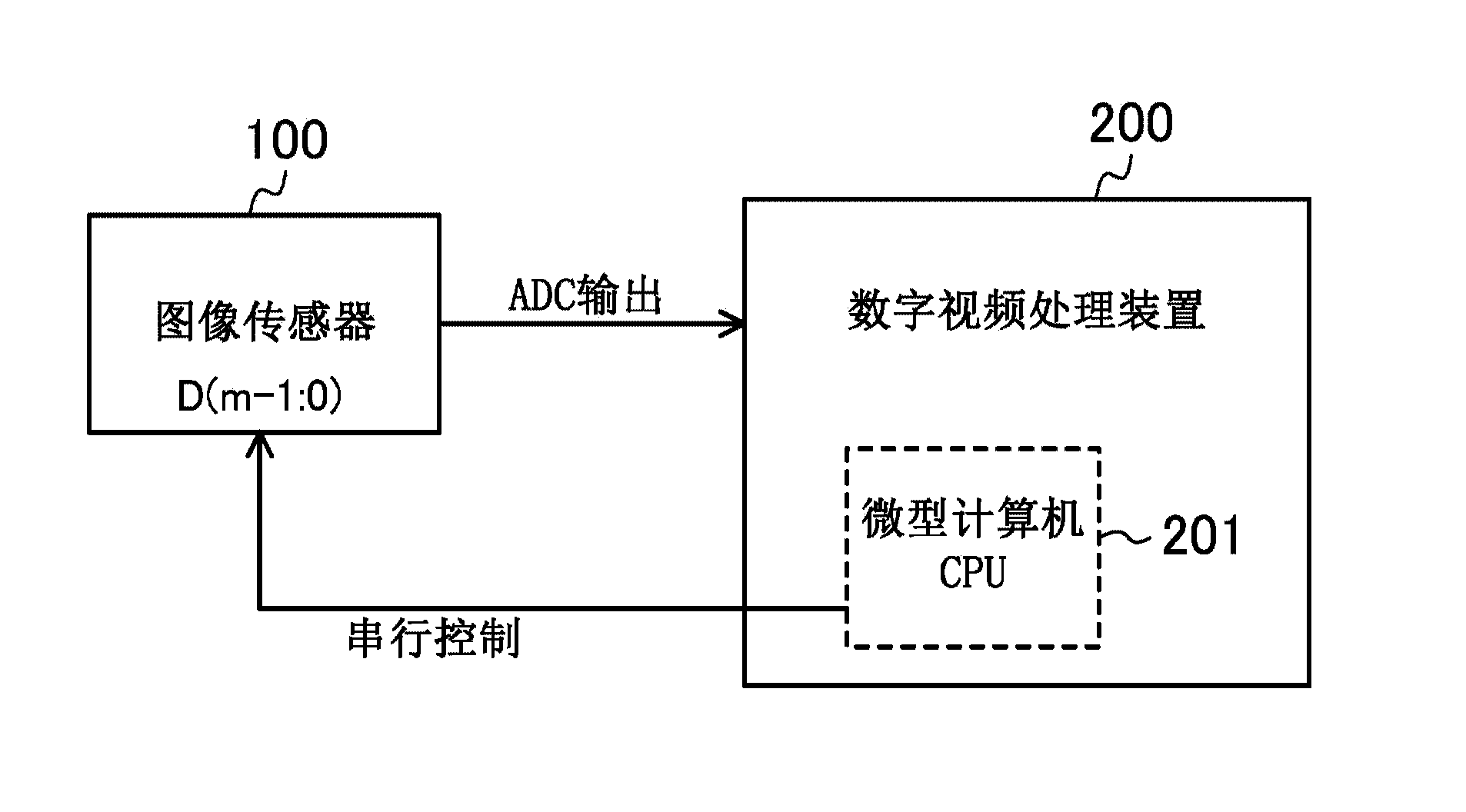

[0076] figure 1 It is a block diagram schematically showing the imaging device according to the first embodiment. exist figure 1 Among them, the camera device includes an image sensor 100 and a digital video processing device 200 .

[0077] The digital video processing device 200 has a microcomputer CPU201, utilizes the serial control signal D(m-1:0) (m is a natural number greater than or equal to 2) from the microcomputer CPU201 to control the image sensor 100, and according to the input from the image sensor 100 The digital signal (ADC output signal) for video signal processing.

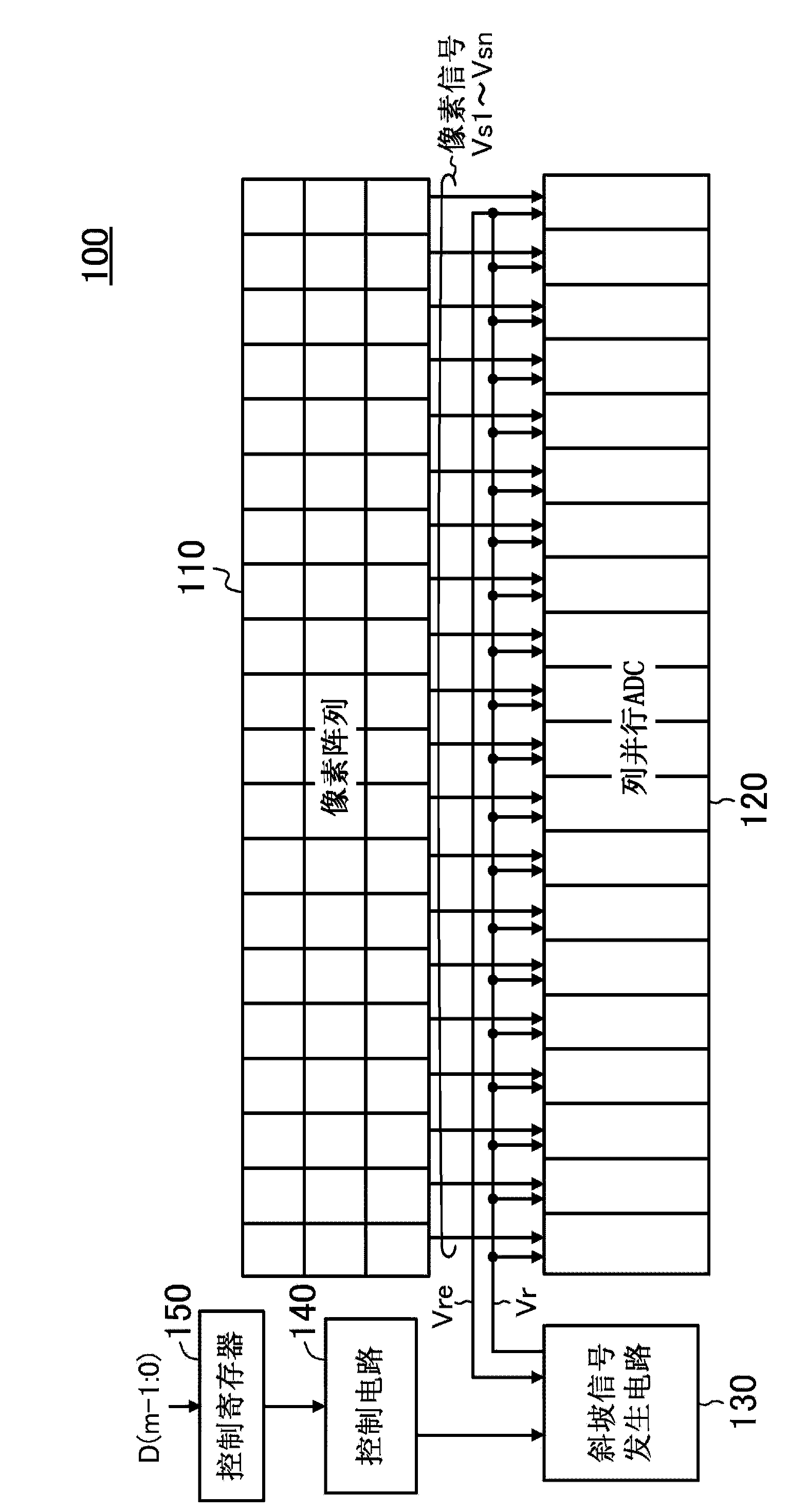

[0078] figure 2 It is a block diagram schematically showing the image sensor 100 according to the first embodiment. exist figure 2 Among them, the image sensor 100 includes: a pixel array 110 , a column-parallel ADC (single-slope ADC) 120 , a ramp signal generating circuit 130 , a control circuit 140 and a control register 150 .

[0079] The pixel array 110 is composed of unit pixels comp...

no. 2 approach >

[0124] Figure 10 It is a diagram showing a configuration example of a ramp signal generating circuit and a connection example of peripheral circuits according to the second embodiment. exist Figure 10 Neutral and Figure 5 The same component labeling and Figure 5 The same symbols are used, and their detailed descriptions are omitted here.

[0125] exist Figure 10 The ramp signal generation circuit 130A with Figure 5 The difference is that a voltage comparison unit 137 is included instead of the time difference comparison unit 132 , and a voltage measurement unit 135 and a reference voltage measurement unit 136 are further included. Here, the calibration of the initializing voltage VE of the control comparator is repeatedly performed during a period in which the image output of the imaging device is invalid, etc. Hereinafter, the calibration performed for the first time will be referred to as the first cycle calibration, and the calibration performed for the second ti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com