Method of improving parallel resistance in photovoltaic cells

A battery and silicon chip technology, applied in the direction of circuits, electrical components, sustainable manufacturing/processing, etc., can solve the problem that selective emitter batteries cannot be applied on a large scale, so as to improve parallel resistance, reduce parallel failure ratio, and improve The effect of conversion efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

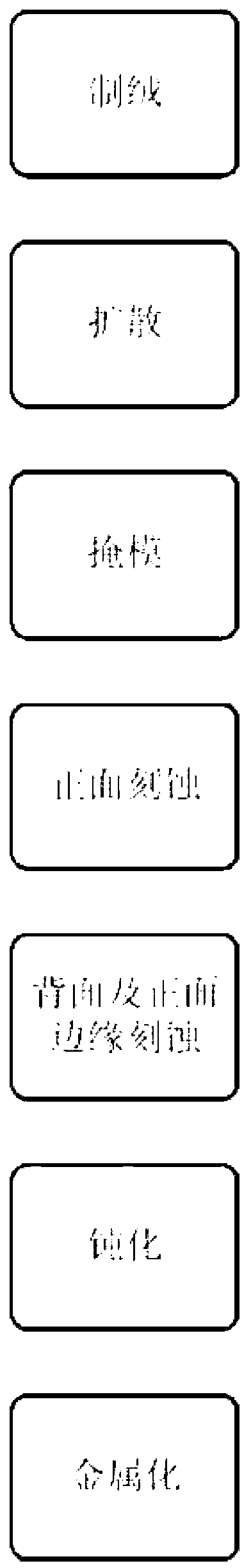

Method used

Image

Examples

experiment example

[0037] Experimental examples and corresponding experimental data are given below.

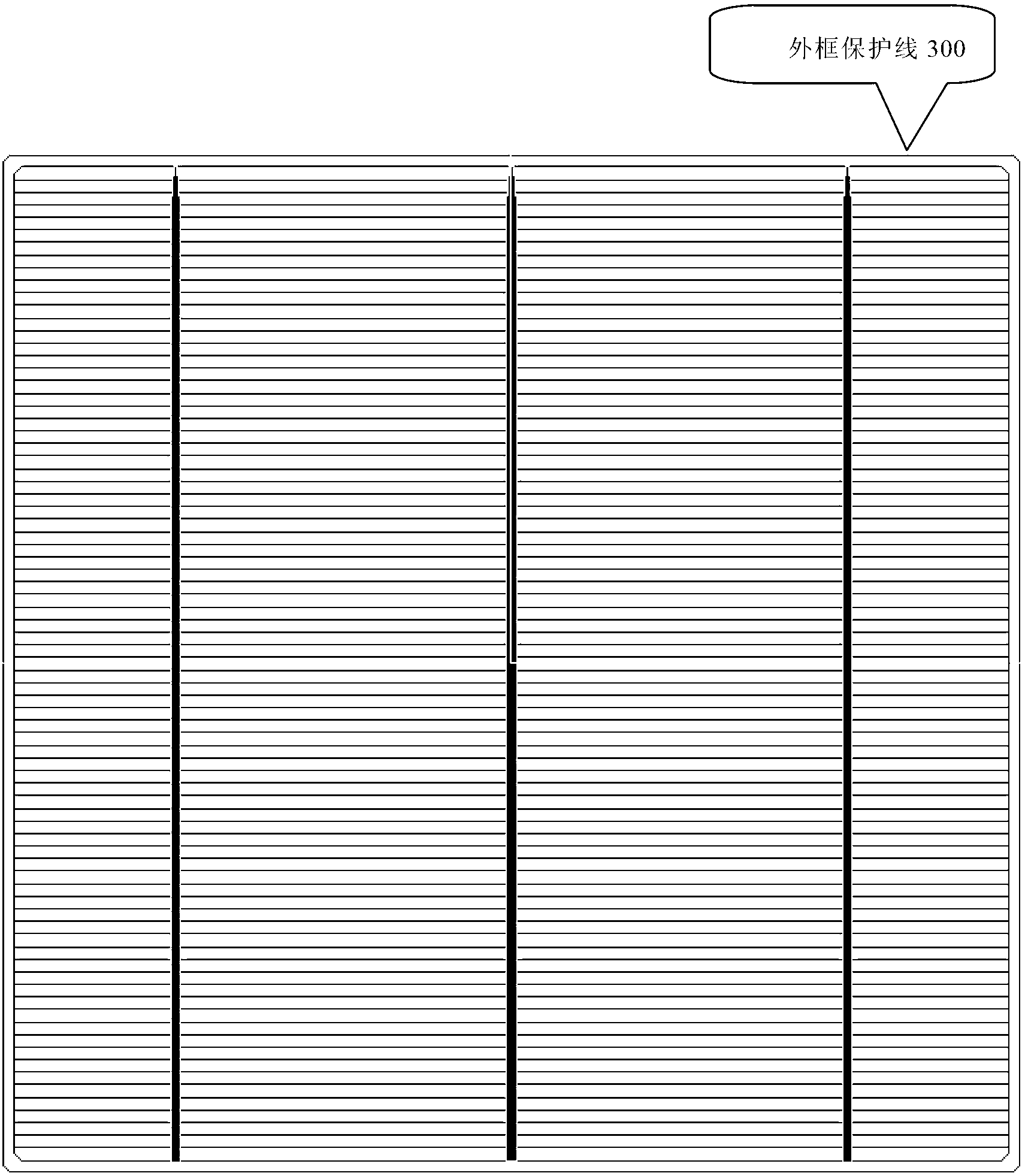

[0038] 1) A batch of polysilicon wafers with a size of 156 mm are acid-textured, and phosphorus is diffused on the front surface. The square resistance after diffusion is 50 ohm / sq. For the film, in addition to adding a mask to the area to be metallized on the front, a mask of a square outer frame is also printed on the edge of the front. The outer frame is 0.2mm away from the edge of the silicon wafer, and the width of the outer frame is 0.25mm.

[0039] 2) Pass the above silicon wafers through HF / HNO in sequence 3 Groove and KOH / BDG groove for surface etching and masking treatment, and then through HCl groove and H 2 Dry the surface with hot air after the O slot. The square resistance of the non-masked area after surface etching is 95ohm / sq.

[0040] 3) Pass the above silicon wafers through HF / HNO in sequence 3Groove and KOH / BDG groove for backside etching and front edge etching, and then...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com