Implementation method of floating point multiply-accumulate unit low in power consumption and high in huff and puff

An implementation method and technology of floating-point numbers, which are applied to calculations using number system representations, calculations using non-contact manufacturing equipment, etc., can solve the problem that the number of floating-point operations per second is far from the peak performance, the throughput rate drops, and the performance Loss and other issues to achieve the effect of avoiding frequent access operations, reducing power consumption, and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Such as figure 1 , 2 As shown, the steps of the implementation method of the floating-point multiplication and accumulation unit with low power consumption and high throughput are as follows:

[0025] 1) Extract and calculate the vector dot multiplication operation The number N, input a pair of operand A and operand B every cycle in N cycles, the first three pipelines perform the floating-point multiplication operation of operand A and operand B to obtain the result of the product, and the result of the product is carried. The form is passed to the next level;

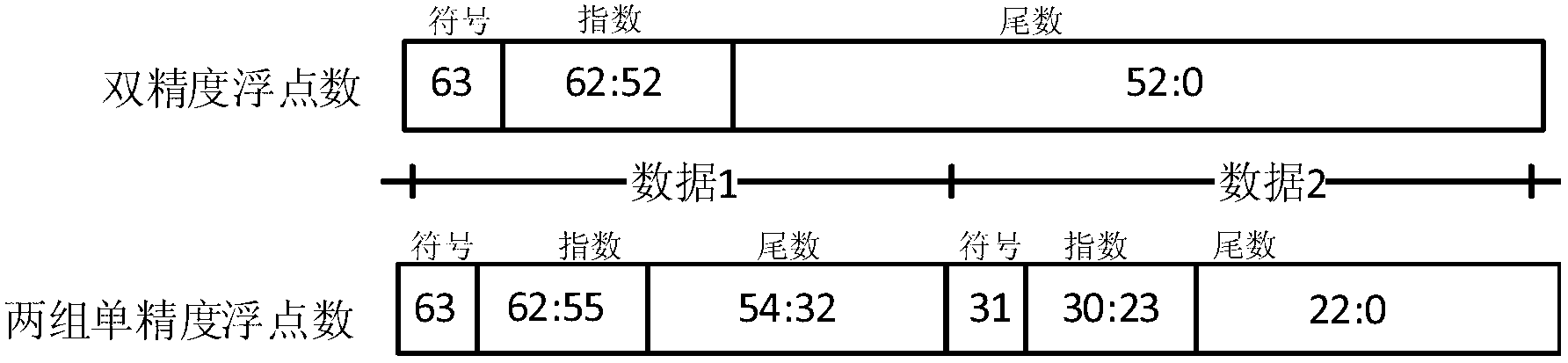

[0026] 2) Expand the bit width of the product in the fourth-stage pipeline, convert the product from base 2 weight to base 64 weight for double-precision floating-point numbers, convert the product from base 2 weight to base 32 weight for single-precision floating-point numbers, and convert the weight After increasing, the bit width of the mantissa increases and the bit width of the exponent decreases;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com