Synthesizable pseudorandom verification method and device for high-speed buffer memory

A technology for high-speed caching and verification methods, which is applied in the detection of faulty computer hardware, functional testing, and the generation of response errors. , The effect of verifying high coverage and ensuring correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

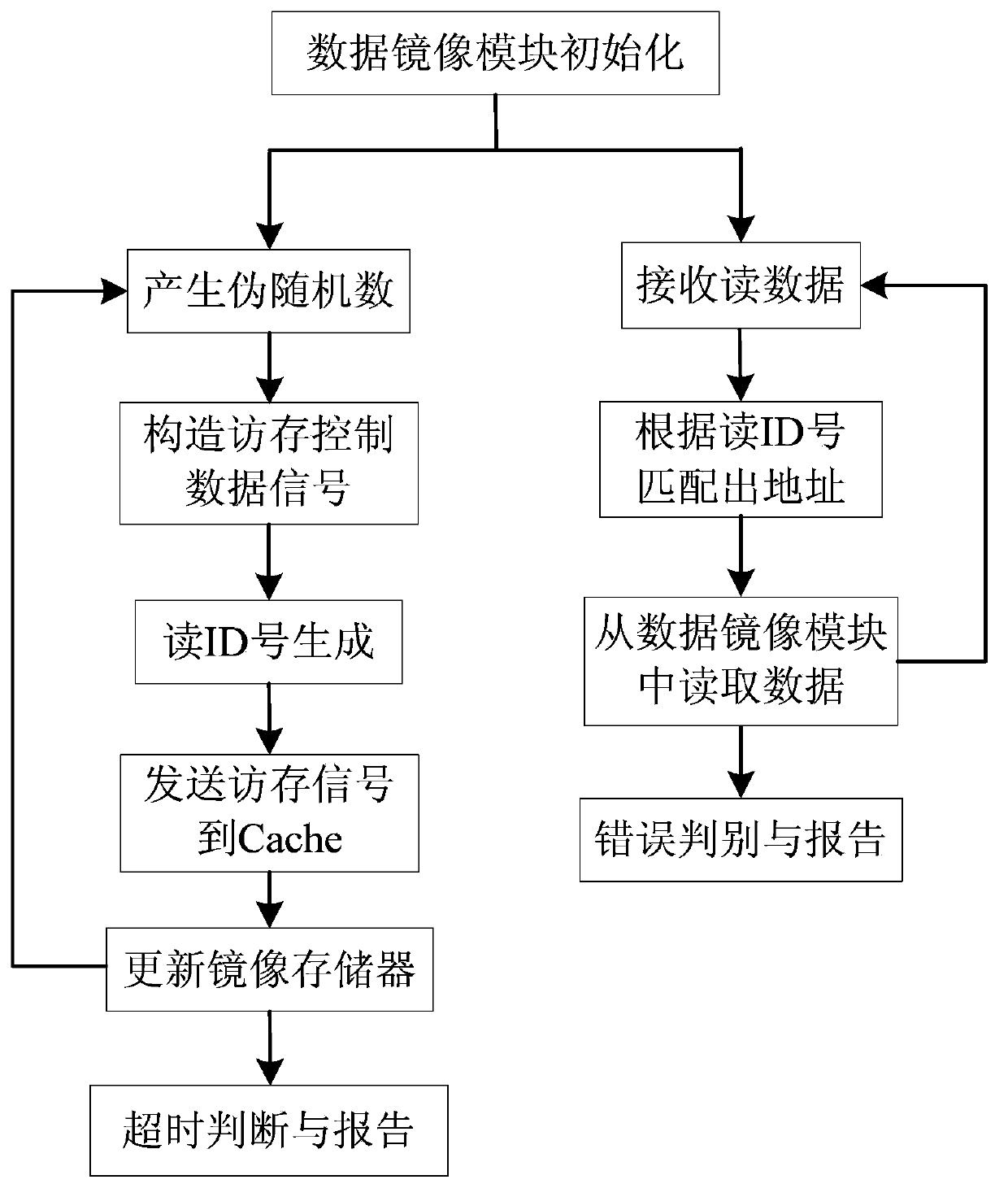

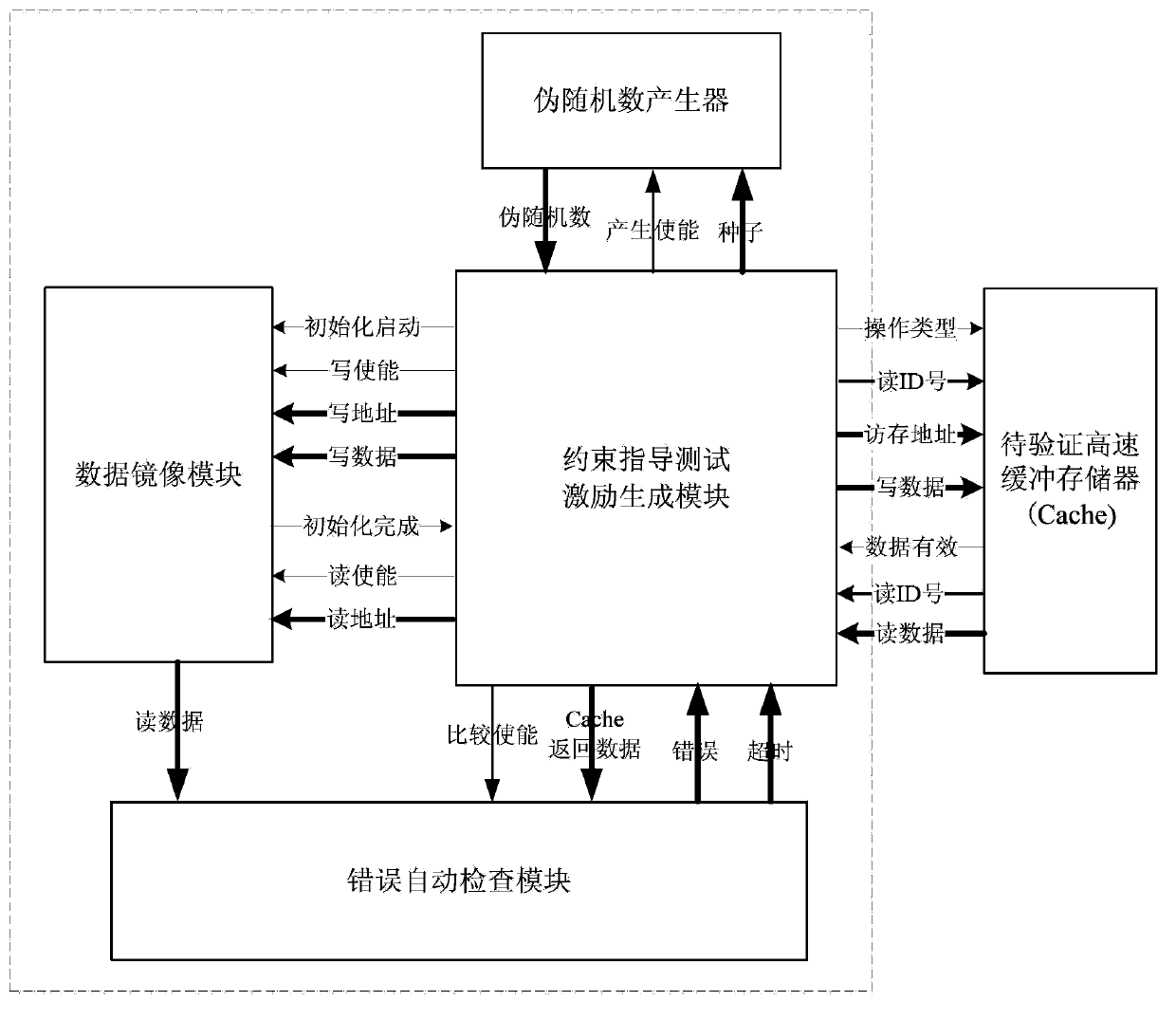

[0055] Such as figure 1 As shown, the implementation steps of the cache-oriented synthesizable pseudo-random verification method in this embodiment are as follows:

[0056] 1) Pre-establish a data mirroring module that performs synchronous write operations with the cache memory, initialize the data mirroring module, and then jump to the next step;

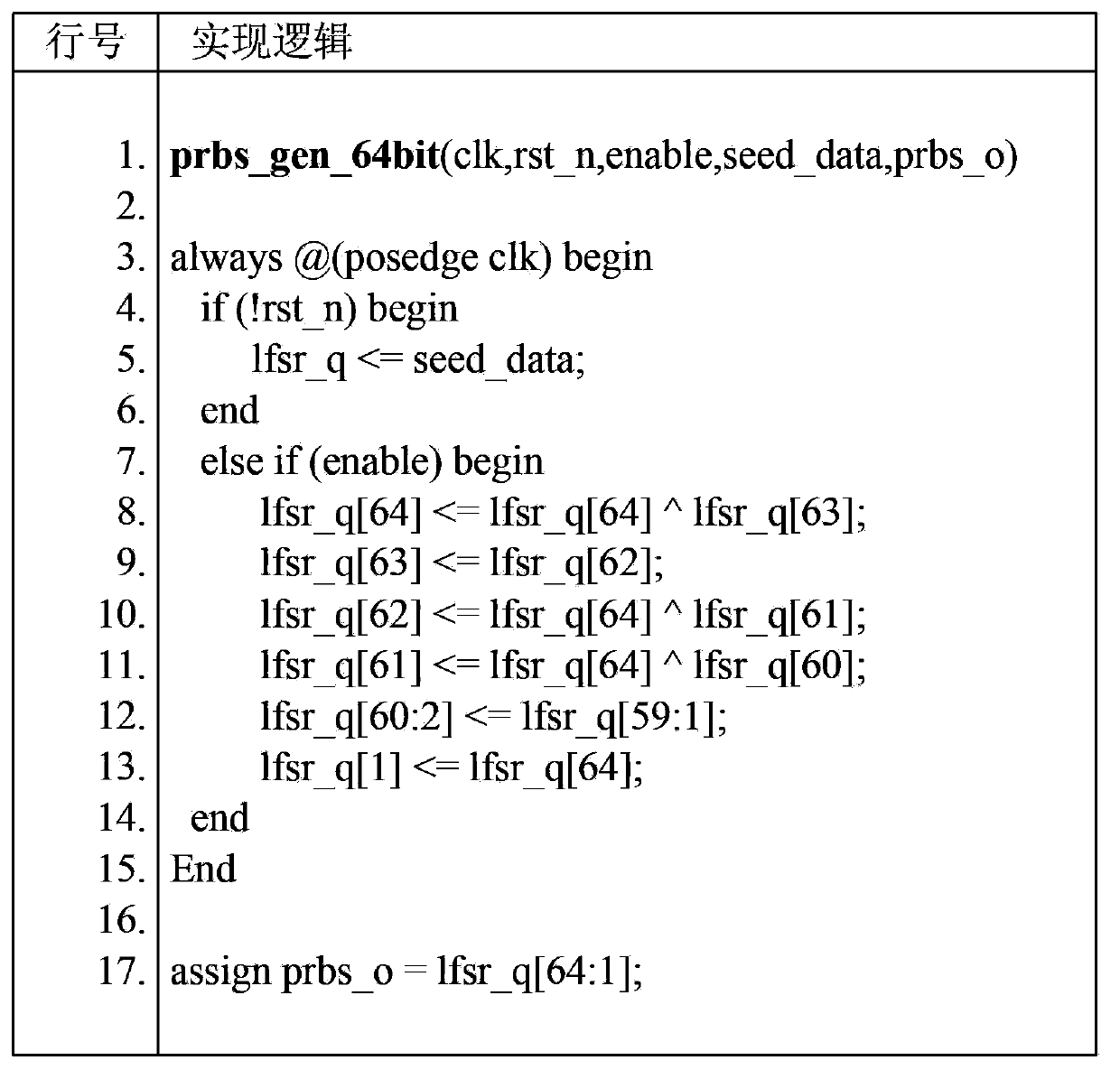

[0057] 2) Generate a pseudo-random number, take out the corresponding bit field from the pseudo-random number, and construct a memory access control data signal for reading or writing the cache memory, if the memory access control data signal is a write operation, then directly The memory access control data signal is sent to the cache memory, and the data mirroring module is updated; if the memory access control data signal is a read operation, then the read identification number (read ID number) is generated, and the memory access address signal and the read ID The number is stored in the read identification number list (read ID...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com