Chip packaging structure of a plurality of assemblies

A chip packaging structure and multi-component technology, applied in the direction of electrical components, semiconductor devices, electric solid devices, etc., can solve the problems of large package thickness and adverse effects on chip performance, achieve thickness reduction, good electrical stability, and avoid negative effects effect of influence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

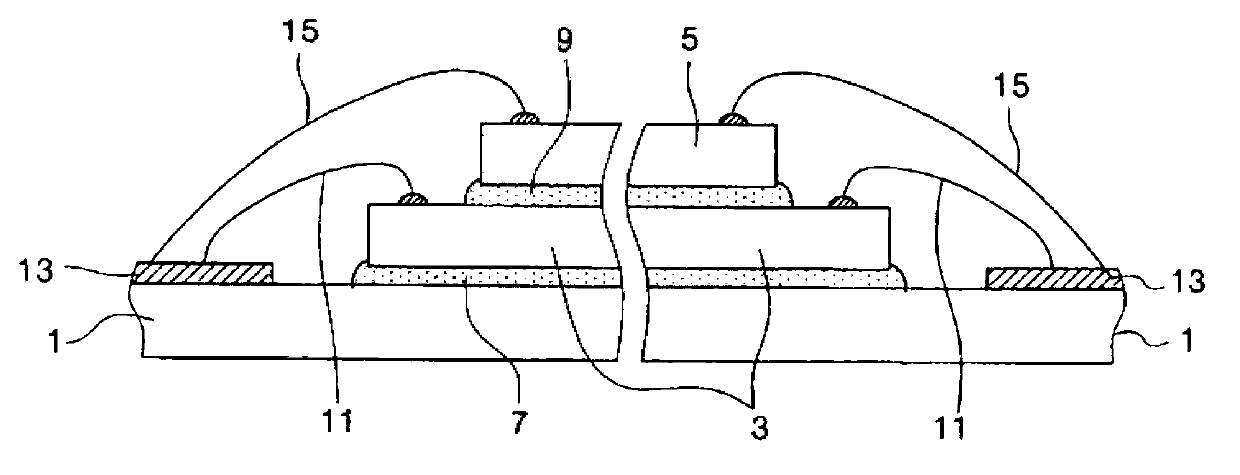

[0029] refer to figure 2 , is a cross-sectional view of the multi-component chip package structure according to the first embodiment of the present invention. In this embodiment, the multi-component chip packaging structure 200 includes a printed circuit board 201 (the first component) on the bottom layer, a chip 204 (the second component) on the printed circuit board 201 , and a chip 204 stacked on the chip 204 chip 205 and inductor 207 (third component). Here, the chip 204, the chip 205 and the inductor 207 are spaced apart from each other and do not touch each other, so as to achieve good electrical isolation. The chip 204 is electrically connected to the printed circuit board 201 through a set of solder balls 202 (first connection structure); the chip 205 and the inductor 207 are electrically connected to the printed circuit board 201 through another set of solder balls 203 located outside the chip 204 .

[0030] Specifically, the chip 205 includes a first straight por...

Embodiment 2

[0036] refer to image 3 , is a cross-sectional view of a multi-component chip package structure according to a second embodiment of the present invention. In this embodiment, the multi-component chip packaging structure 300 includes a lead frame 301 (first component) on the bottom layer, a chip 304 (second component) on the lead frame 301 , and an inductor stacked on the chip 304 306 (third component). Wherein, the chip 304 is connected to the lead frame 301 through a group of bumps 302 (first connection structure).

[0037] The connection between the inductor 306 on the upper layer and the lead frame 301 is realized through the following connection methods:

[0038] The lead frame 301 is arranged in a bent shape, which includes a second straight portion 301-1 and a second bent portion 301-2; the second bent portion 301-2 is located in the outer area of the chip 304 and is separated from the chip 304, Its first end is connected to the second straight line portion 301 - 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com