Black box logic verification method for physical chip layout

A logic verification, chip technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as power supply and ground short circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

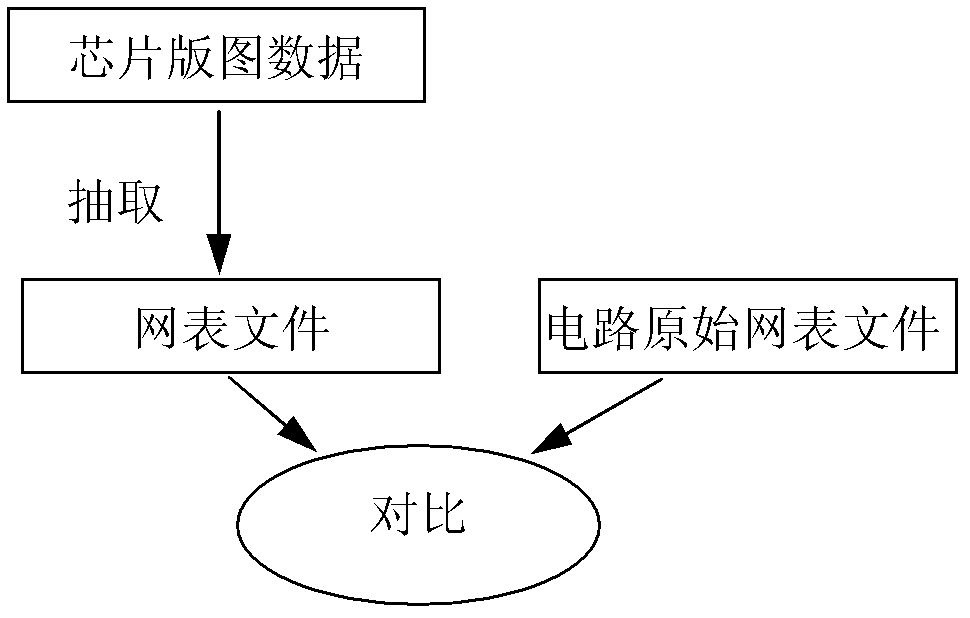

[0023] Such as Figure 4 As shown, the black box logic verification method of the chip physical layout of the present invention is an improvement to the prior art BLACK BOX LVS (black box layout logic comparison) method, comprising the following steps:

[0024] The first step is to use the existing technology to conduct BLACK BOX LVS inspection on the chip;

[0025] The second step is to establish each process level library; through the established process level library, find out the information of the metal layer of the process and the information of the forbidden wiring layer, and store the information of each process metal layer and the information of the forbidden wiring layer, so that the program can use proceed to the next steps;

[0026] The third step is to read the GDSII data of the chip, and use the prohibited wiring layer as the identification feature to identify the position and name of each other party's IP in the chip;

[0027] The IP of the other party can be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com