Improved oxide-film resistance changing memory and improvement method thereof

A technology of resistive variable memory and oxide thin film, which is applied in the direction of electrical components, etc., can solve the problems of fatigue, stability and uniformity obstacles of new resistive variable memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

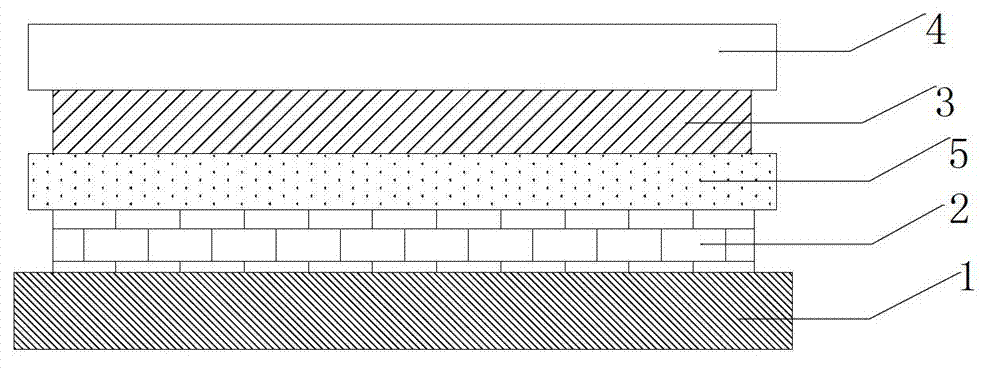

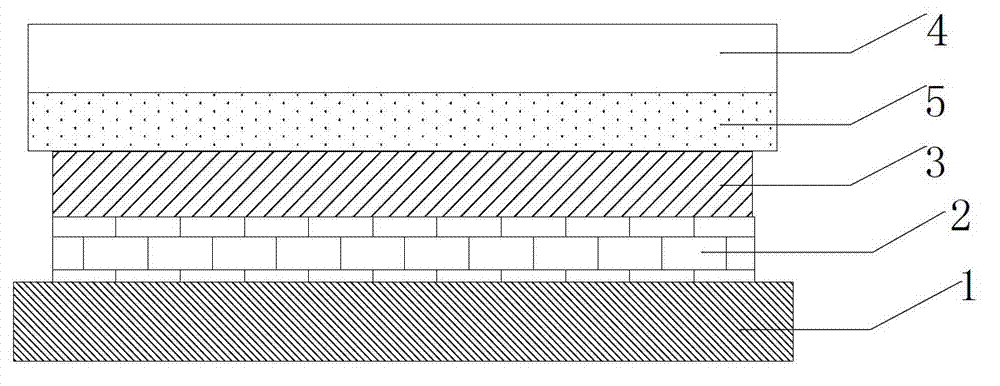

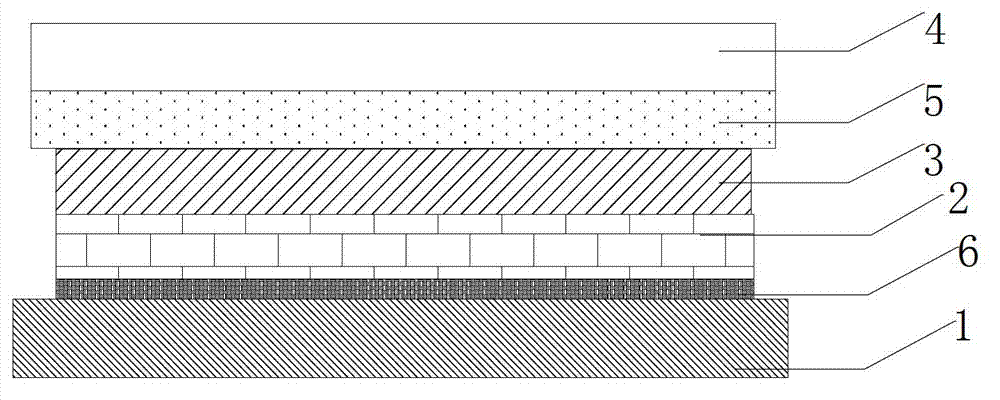

[0043] Example 1 Preparation of Improved Oxide Thin Film Resistive Variable Memory

[0044] method one:

[0045] In SiO 2 On the Si insulating substrate, a 10nm adhesion layer Ti, a 50nm bottom electrode W, and a 100nm metal oxynitride interface layer WO were sequentially deposited by magnetron sputtering. 0.1 N 0.8 , 40nm oxide resistive layer TaO 1.8 , 50nm top electrode Pt, and the obtained RRAM is marked as memory A.

[0046] Method Two:

[0047] Using the same deposition method and materials as method one to prepare a device without a metal oxynitride interface layer, the steps are: on SiO 2 On the / Si insulating substrate, a 10nm adhesion layer Ti, a 50nm bottom electrode W, and a 40nm oxide resistive layer TaO were sequentially deposited by magnetron sputtering 1.8 , 50nm top electrode Pt, prepared and obtained a resistive variable memory with a sandwich structure of "bottom electrode / oxide film / top electrode" as a control, marked as memory A'.

[0048] Method th...

Embodiment 2

[0054] Example 2 Performance testing of oxide thin film resistive memory

[0055] 1. Efficiency detection of RRAM

[0056] Take the memory A of the first method and the memory A' of the second method in Example 1, and perform DC voltage scanning detection. The experimental results are shown in the current-voltage (I-V) curve diagram of the DC voltage scanning (attached Figure 3-4 ), including the initial soft breakdown (forming), high-impedance state (RESET), and low-impedance state (SET) operation. in image 3 is the I-V curve of a memory device with an interfacial layer, Figure 4 is the I-V plot of a memory device without an interfacial layer.

[0057] Depend on Figure 3-4 The experimental results show that the RESET current of the storage device with the interface layer is small (1 mA), while the RESET current of the storage device without the interface layer is relatively large (about 40 mA). Since the device is easily damaged by a large current, a memory device wi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com