Electro static discharge protective circuit for circuit board interface

An electrostatic discharge protection, electrostatic discharge protection technology, applied in the field of electrostatic protection of circuit boards, can solve problems such as difficult protection ability, large TVS area, and difficulty in meeting the design requirements of radio frequency interfaces

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

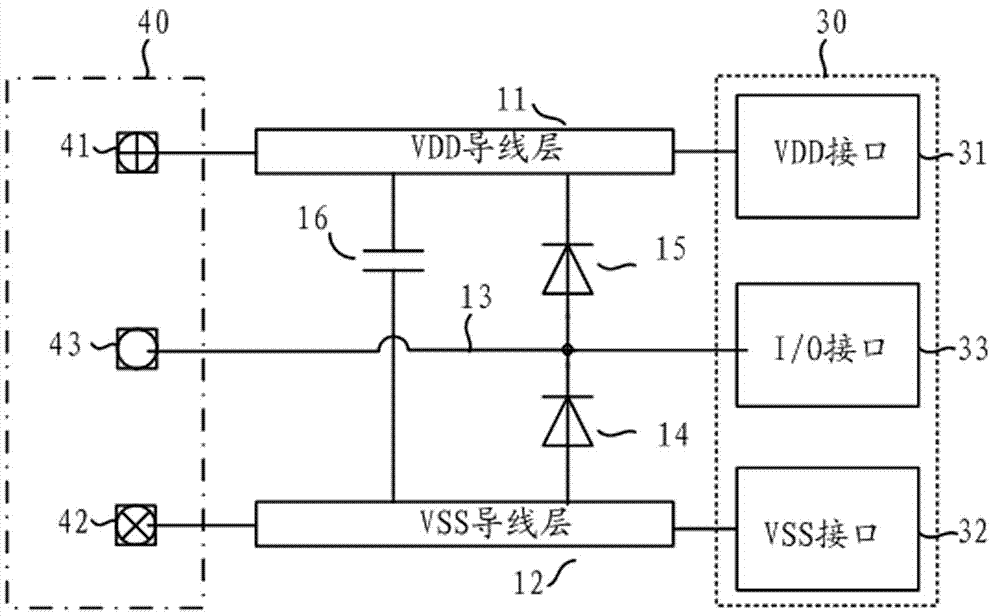

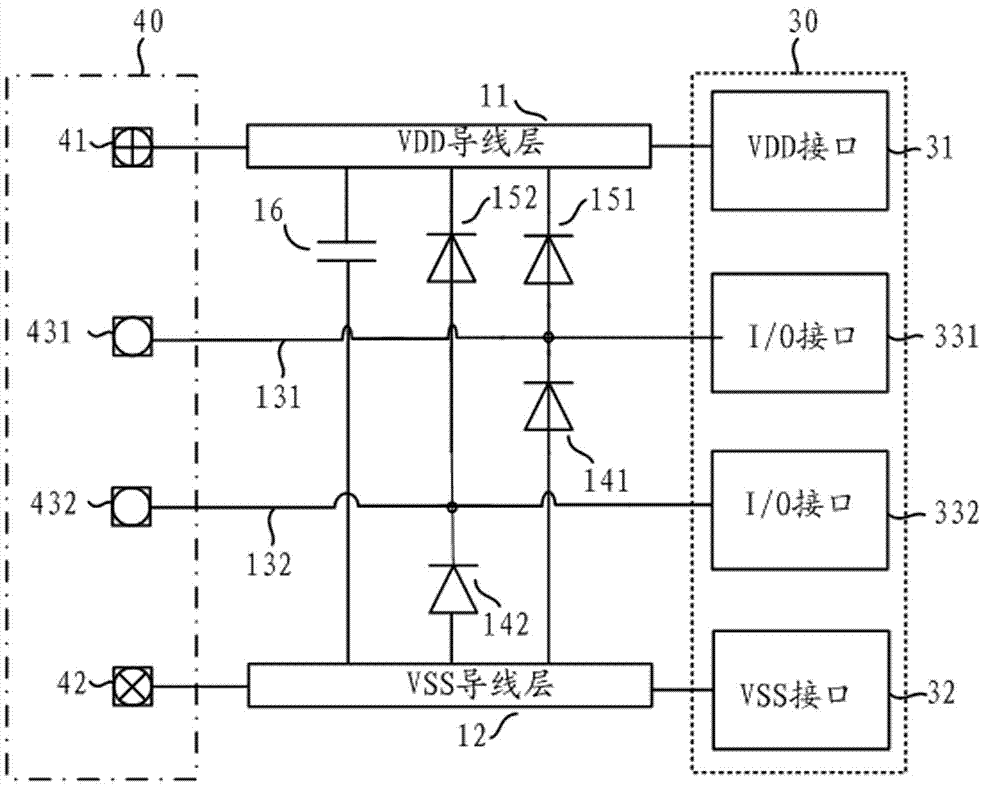

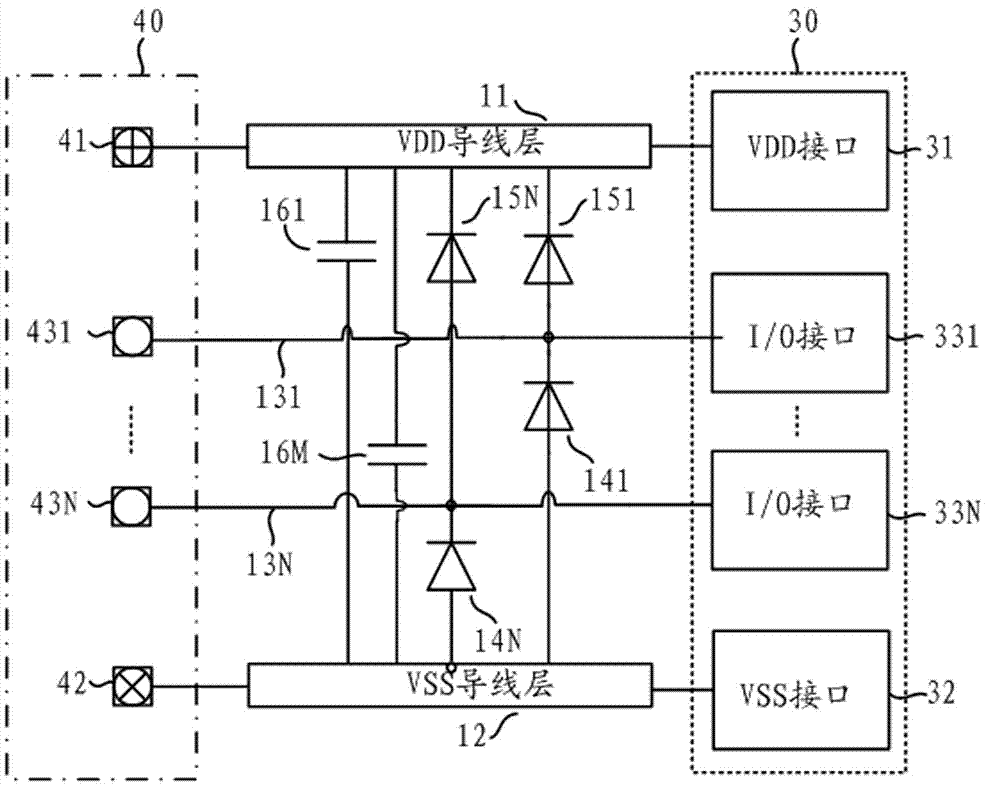

[0042] Such as figure 1 As shown, the circuit board interface electrostatic discharge protection circuit of the present invention includes a high-voltage wire layer 11 and a low-voltage wire layer 12; a capacitor 16 is electrically connected between the high-voltage wire layer and the low-voltage wire layer; the signal interface 33 (I / O interface) and The signal terminal 43 of the protected circuit 40 is connected together through the signal line 13; between the signal line 13 and the high voltage conductor layer 11, there is provided a first diode 15 whose polarity is forward biased from the signal line 13 to the high voltage conductor layer 11, That is, the anode of the first diode 15 is connected to the signal li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com