Software-hardware co-verification platform

A software-hardware collaboration and verification platform technology, applied in the detection of faulty computer hardware, functional testing, etc., can solve the problems of limited capacity, high cost, and lengthy hardware debugging cycle, so as to accelerate the development process, avoid lengthy cycles, reduce cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

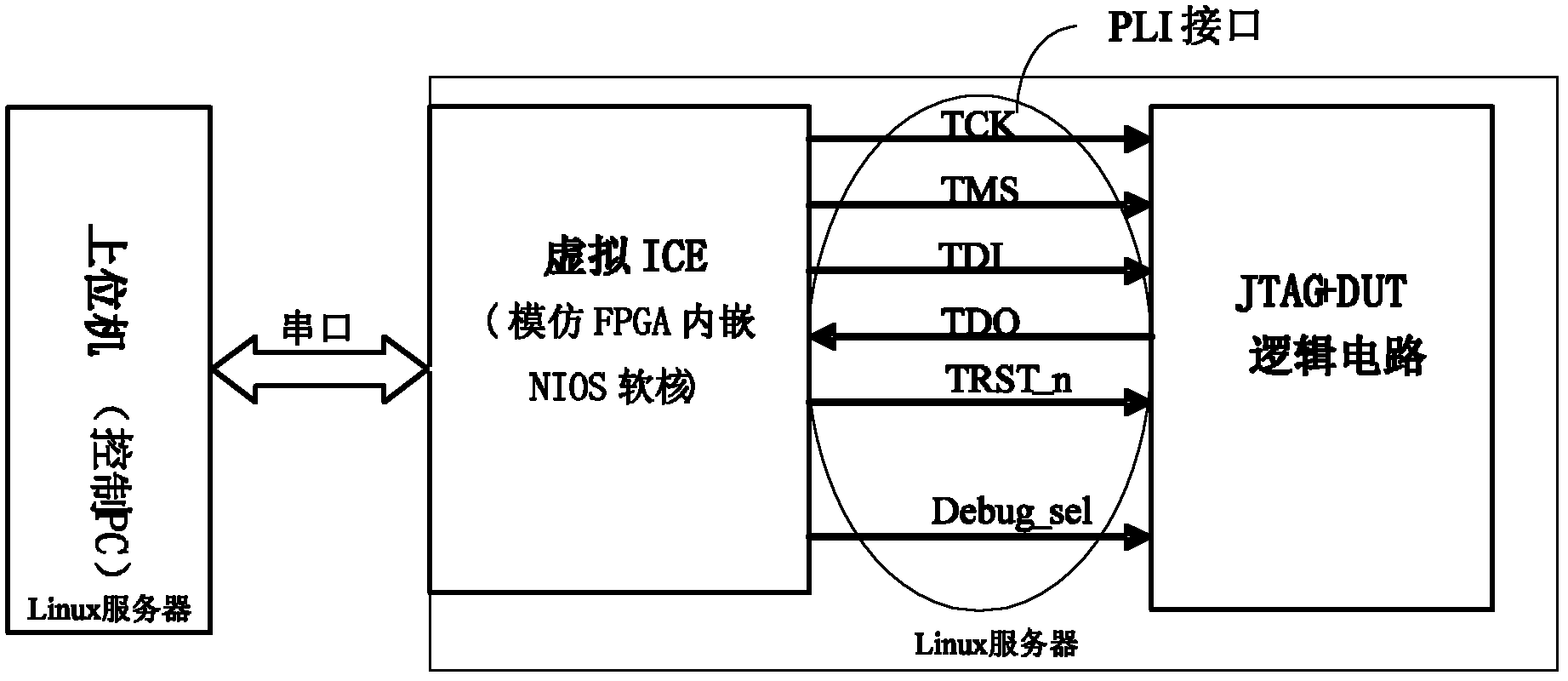

[0012] Such as figure 1 Described, a kind of software-hardware co-verification platform, comprises upper computer, virtual online emulator ICE and tested design DUV and communication part, the communication between virtual online emulator ICE and upper computer is through the serial port between the server, and The test and design DUVs are connected by the programming language interface PLI, in which the upper computer is implemented on a server installed with a Linux operating system, and the virtual online emulator ICE, PLI interface, and the tested design DUV are implemented on another server installed with a Linux operating system. implemented on the server.

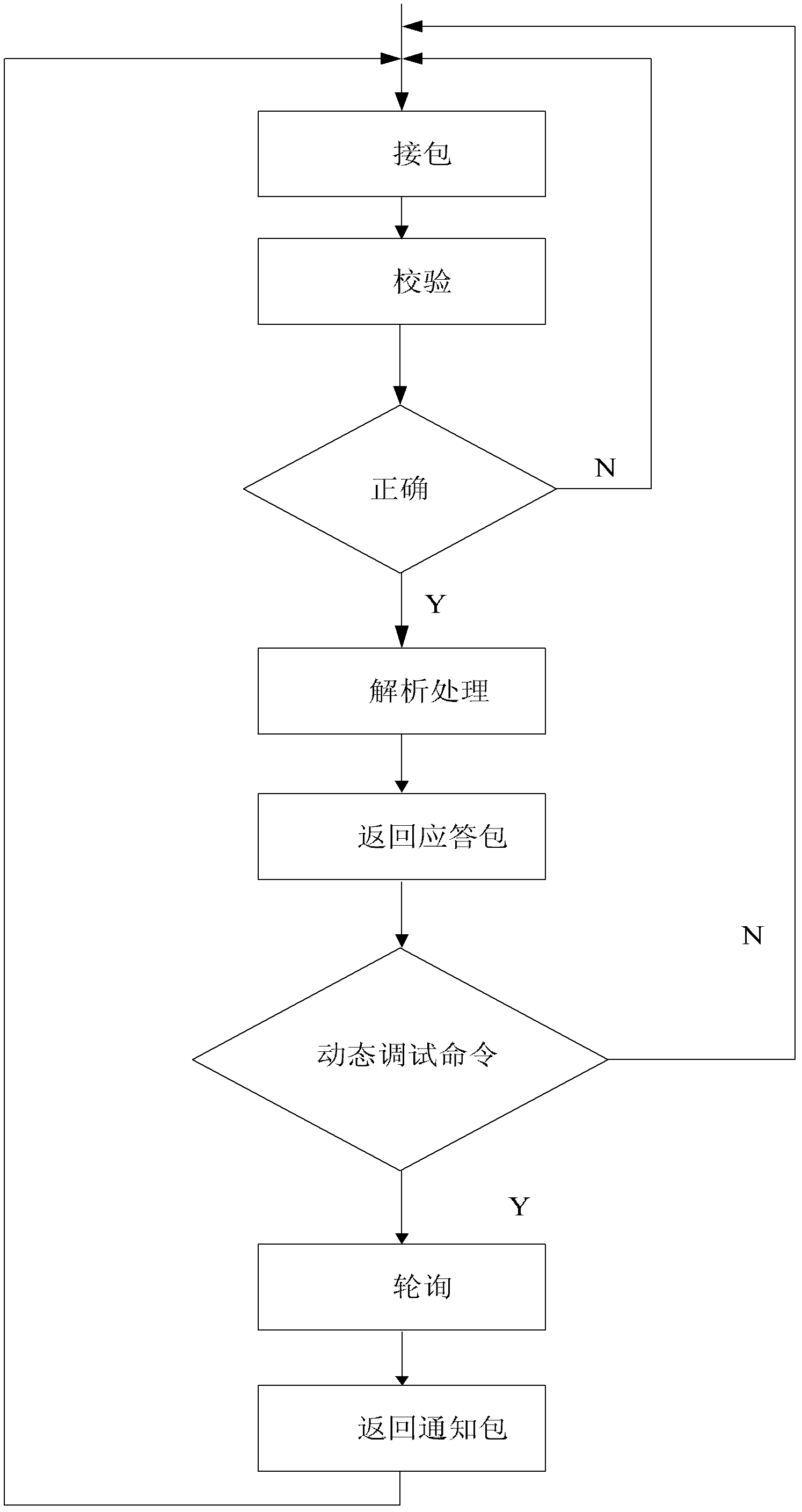

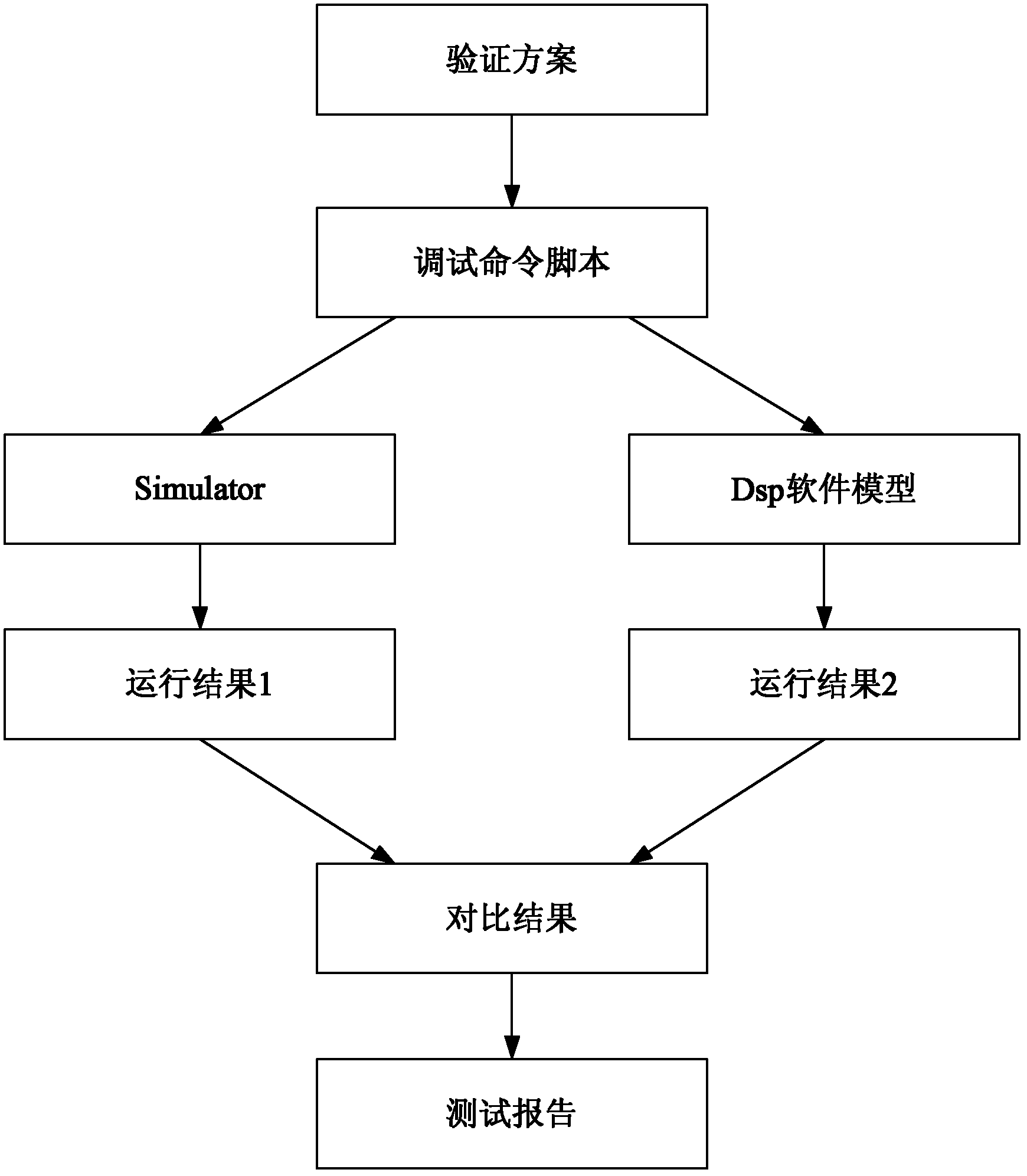

[0013] The upper computer mainly completes the work of generating verification data and comparing verification results; the virtual ICE is a C code program that completely imitates the functions realized by the online emulator, and is the core part of the entire test platform. The serial port and the programming lan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com