PCB (printed circuit board) packaging architecture method

A packaging library and mounting hole technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of prolonging the design cycle, increasing the design workload, increasing the complexity of PCB design and error rework rate, etc., to achieve Reduce duplication of work, facilitate layout and wiring design, reduce the effect of error rate and rework rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0037] Such as figure 1 As shown, the PCB packaging architecture method of the present embodiment includes the following steps:

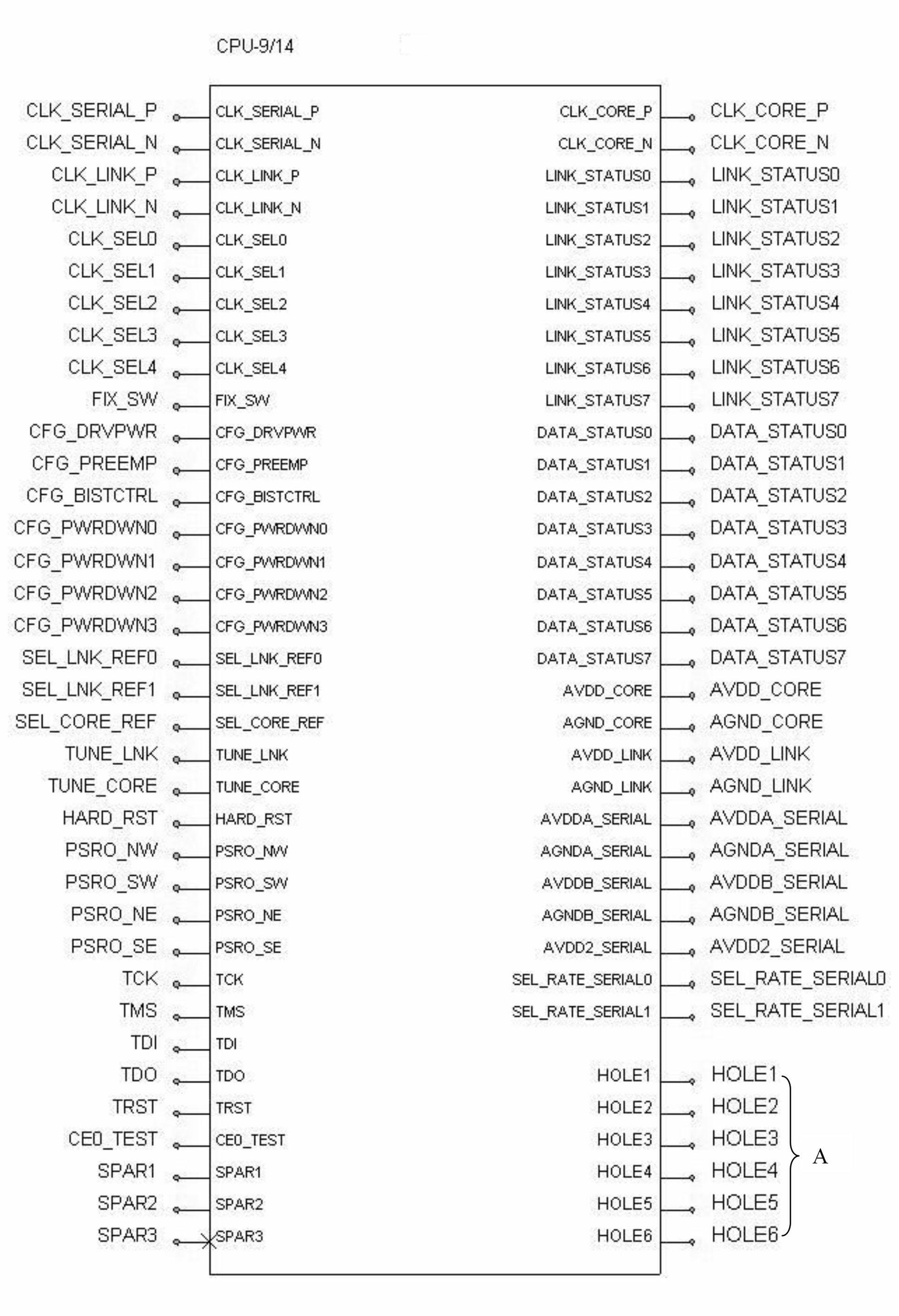

[0038] 1. If image 3 As shown, a logic symbol is established in the logic symbol library, which includes the pins and mounting holes of the component and its auxiliary components. Among them, the auxiliary components of the components include: heat dissipation components, positioning components and structural firmware. The aforementioned logic notation (see image 3 ) is in the case of figure 2 The traditional logic symbol of the component is made by adding the logic of the pins and mounting holes of the auxiliary component, image 3 Middle A is the logic of mounting holes and positioning holes required for structure and heat dissipation.

[0039] 2. Establish traditional packaging symbols for components (such as Figure 4 shown), and then establish an auxiliary packaging symbol according to the structural characteristics of the auxiliary co...

Embodiment 2

[0044] Such as Figure 6 As shown, the PCB package architecture method of the present invention comprises the following steps:

[0045] 1. Create a traditional logic symbol of a component in the logic symbol library (such as Figure 7 shown); create a new auxiliary logic symbol required by the auxiliary component of the component (such as Figure 8 As shown), the auxiliary logic symbols include the logic of the pins and mounting holes of the auxiliary components of the component, and the traditional logic symbols are automatically associated with the auxiliary logic symbols. Among them, the auxiliary components of the components include: heat dissipation components, positioning components and structural firmware, etc.

[0046]2. Establish traditional packaging symbols for components (such as Figure 9 shown), and then create an auxiliary packaging symbol according to the structural characteristics of the auxiliary components of the component (such as Figure 10 shown), the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com