Digital video interface data recovery circuit

A technology of digital video interface and recovery circuit, which is applied in the direction of TV, electrical components, color TV, etc., can solve the problem of insufficient stability of digital phase-locked loop, reduce the bit error rate of data transmission, etc., and achieve the solution of possible instability and reduce bit error rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] The present invention will be further elaborated below in conjunction with the accompanying drawings.

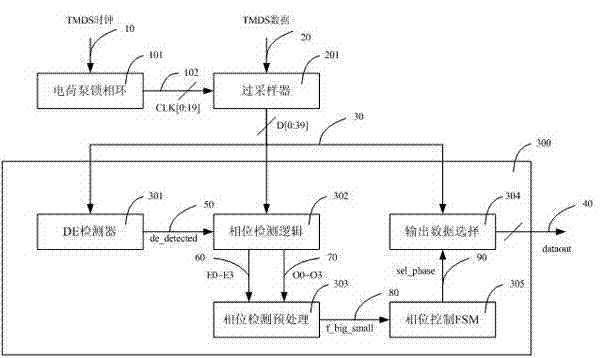

[0062] like figure 1 As shown, a digital video interface data recovery circuit, the circuit includes a charge pump phase-locked loop 101, an oversampler 201, and a data recovery unit 300. Wherein, the data recovery unit 300 includes a DE detector 301 , a phase detection logic unit 302 , a phase detection preprocessing unit 303 , an output data selection unit 304 , and a phase control FSM 305 .

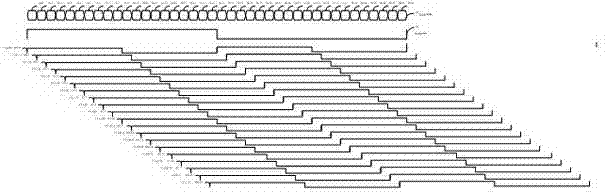

[0063] The charge pump phase-locked loop 101 receives the TMDS clock signal 10 and outputs a 20-phase clock signal CLK[0:19] 102 twice the frequency of the TMDS clock. The oversampler 201 receives the TMDS data signal 20, and the sampling clock is a 20-phase clock CLK[0:19] 102 twice the frequency of the TMDS clock. In one TMDS clock cycle, the oversampler outputs 40-bit parallel data D[0: 39] 30, that is, one TMDS data is sampled four times.

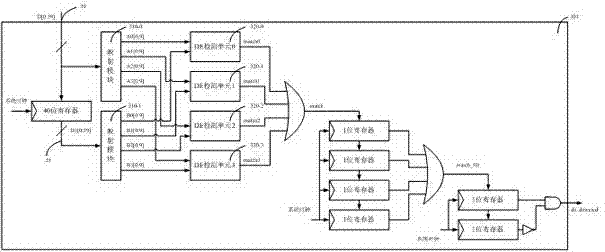

[0064] The DE detector 301 re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com