Cache handling device in multi-channel multi-phase filter

A polyphase filter and cache processing technology, applied in the filter field, can solve problems such as time redundancy, fixed coefficients, waste of BRAM resources, etc., and achieve the effect of saving BRAM resources and reducing the number of uses

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

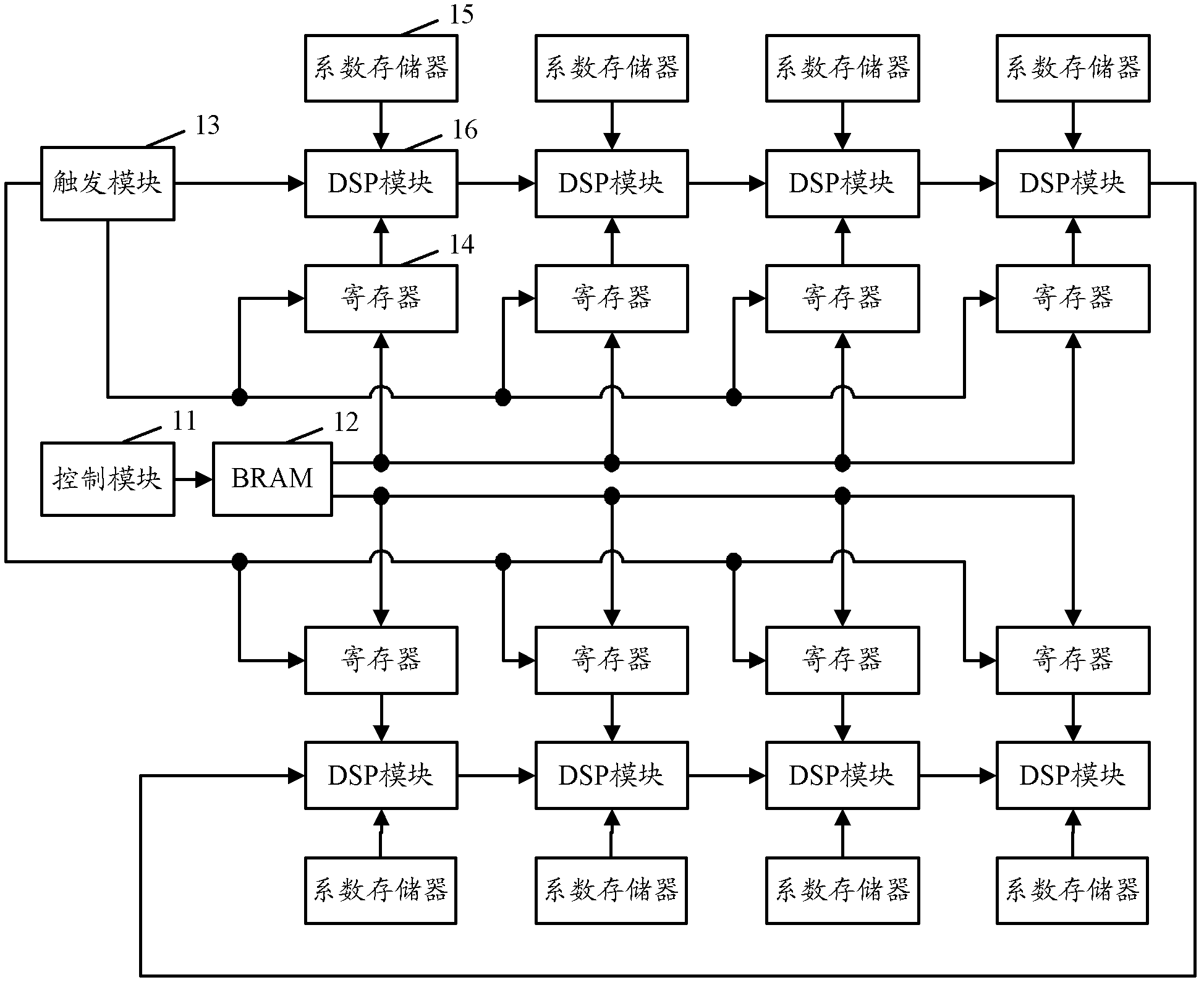

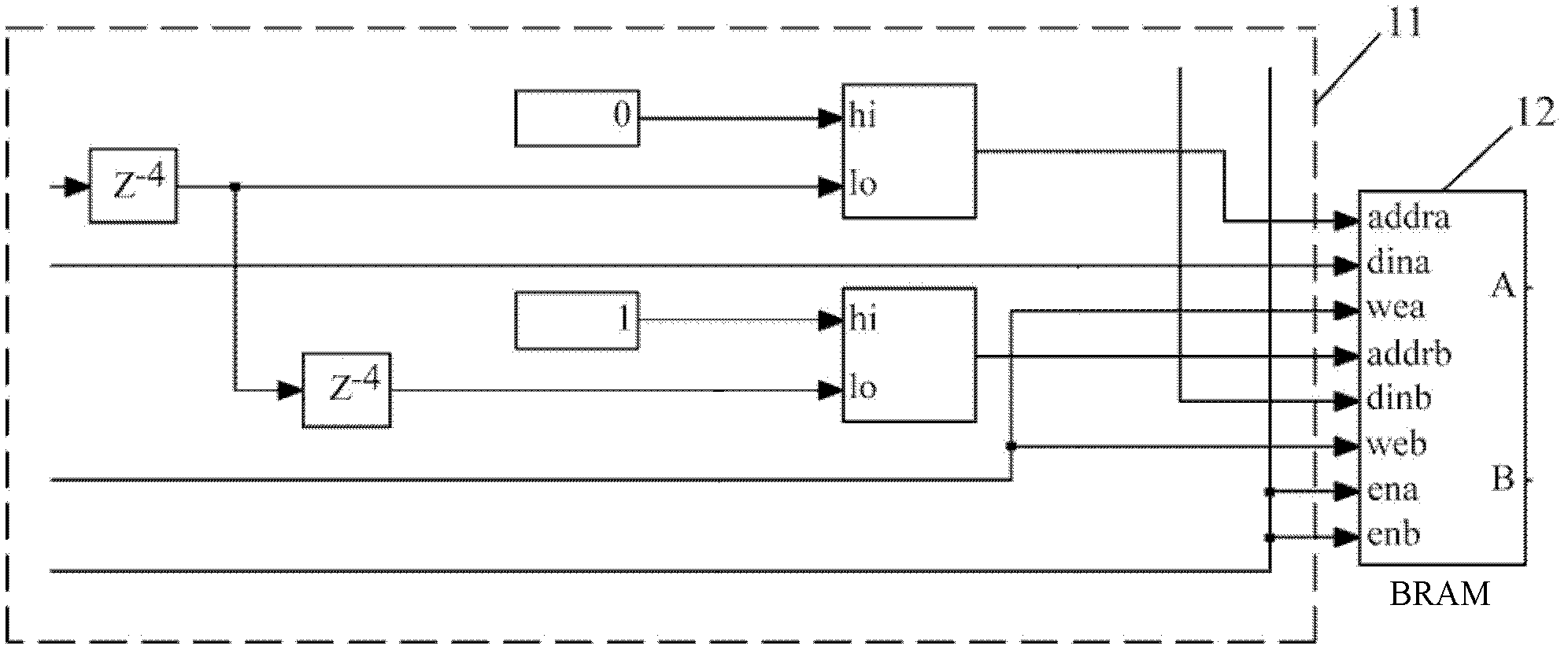

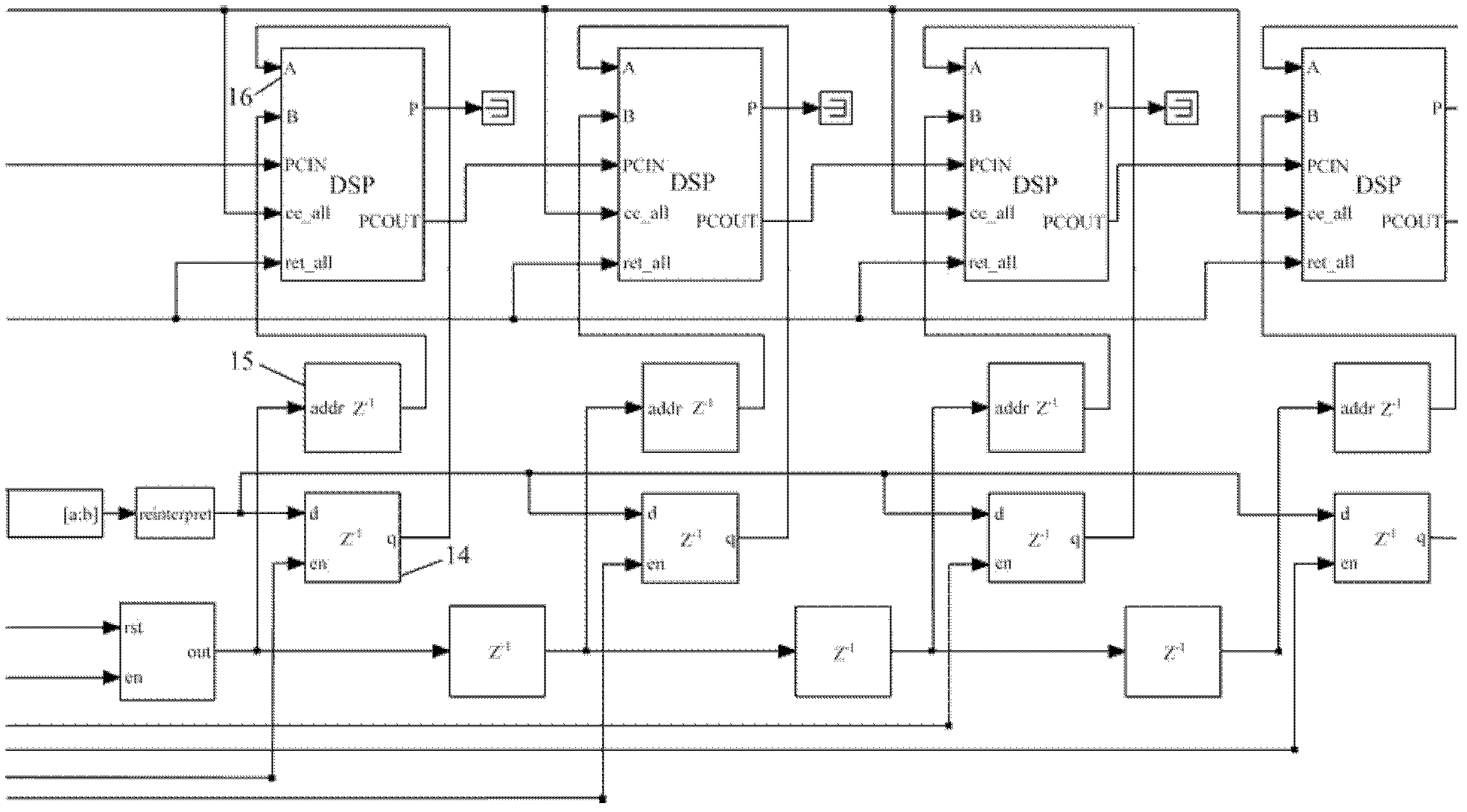

[0019] The cache processing device in the multi-channel polyphase filter in the embodiment of the present invention includes a control module, a BRAM, a trigger module, several registers, several coefficient memories and several cascaded DSP modules, and the registers, coefficients The number of memories and DSP modules is the same, and each level of DSP modules corresponds to different registers and coefficient memories. Preferably, the number of DSP modules is 6 or 8. Taking the number of DSP modules as 8 as an example, the buffer processing device in the multi-channel polyphase filter of the present invention will be described in detail in conjunction with the accompanying drawings.

[0020] figure 1 It is a structural schematic diagram of an embodiment of the device of the present invention.

[0021] see figure 1 As shown, the cache processing device in the multi-channel polyphase filter in the embodiment of the present invention includes a control module 11, a BRAM 12,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com