Method and device for accelerating emulation of CMP (Chemical Mechanical Polishing)

A technology of simulating data and grids, applied in the fields of instrumentation, calculation, electrical and digital data processing, etc., can solve the problems of restricting design efficiency, time-consuming, slow speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

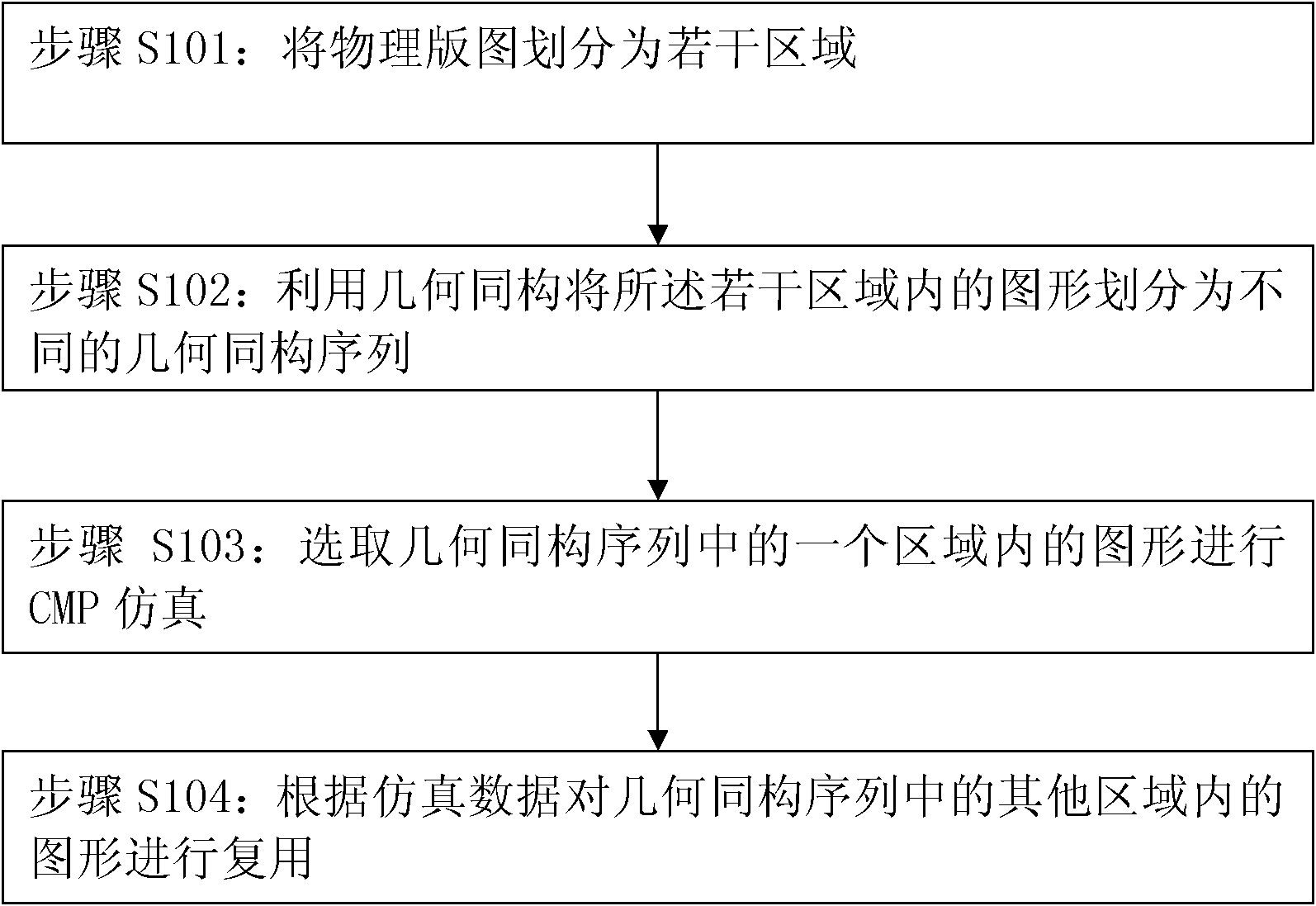

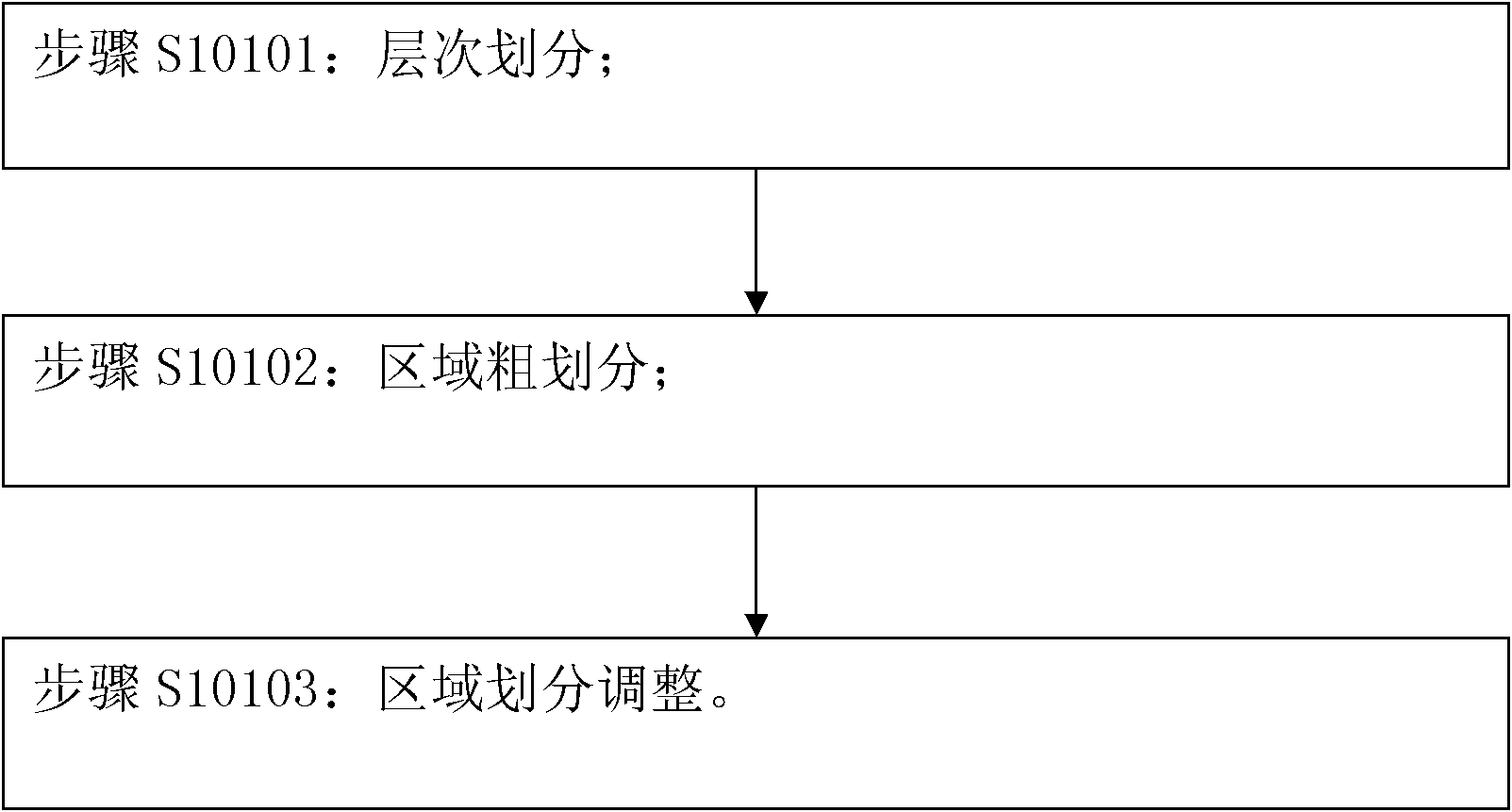

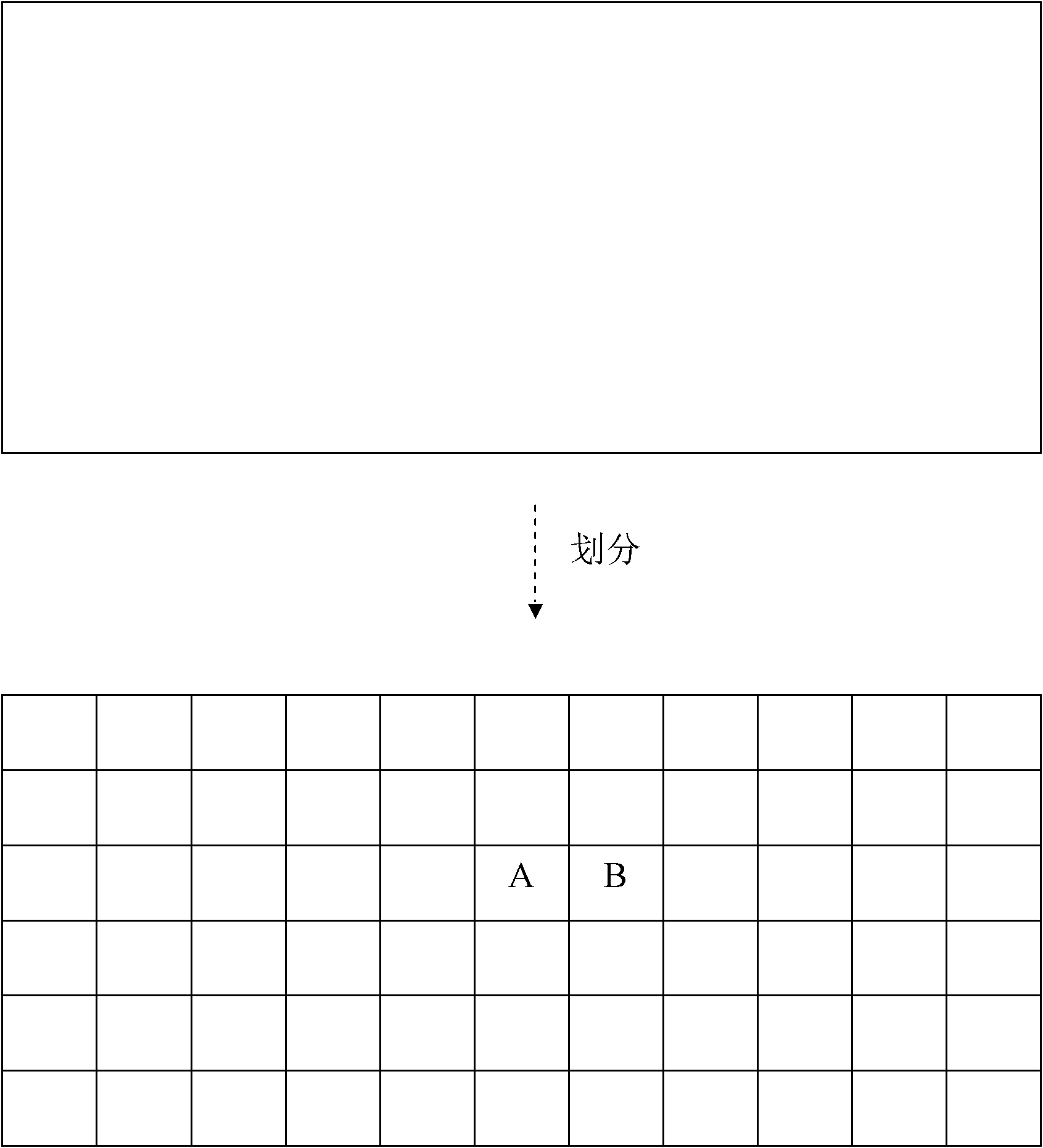

[0041] In the physical design of integrated circuits, there is a great similarity in the design graphics between local areas, which determines the sameness of the CMP calculation process and calculation results between local areas, and the multiplexing of calculation results can effectively reduce the Complicated simulation calculation tasks can improve the overall CMP simulation speed of the chip without sacrificing simulation accuracy. The present invention performs CMP simulation on different regions in a parallel manner to improve the CMP simulation speed of the whole chip and shorten the time required for the whole chip by dividing the physical layout area, the geometric isomorphism of the graphics in the area, the CMP simulation in the area, and the multiplexing of the area CMP simulation data. The CMP simulation time of the whole chip; the CMP simulation tasks are merged in the way of graph isomorphism, and the CMP simulation tasks of the same physical layout are calcula...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com