Reset circuit of anti-fuse type FPGA (Field Programmable Gate Array) system

A system reset and anti-fuse technology, applied in the direction of electrical components, electronic switches, pulse technology, etc., can solve the problems of anti-fuse FPGA asynchronous reset, internal register automatic configuration, inapplicability, etc., to eliminate competition risks , remove jitter, realize the effect of asynchronous reset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] A kind of antifuse type FPGA system reset circuit of the present invention is introduced below in conjunction with accompanying drawing and embodiment:

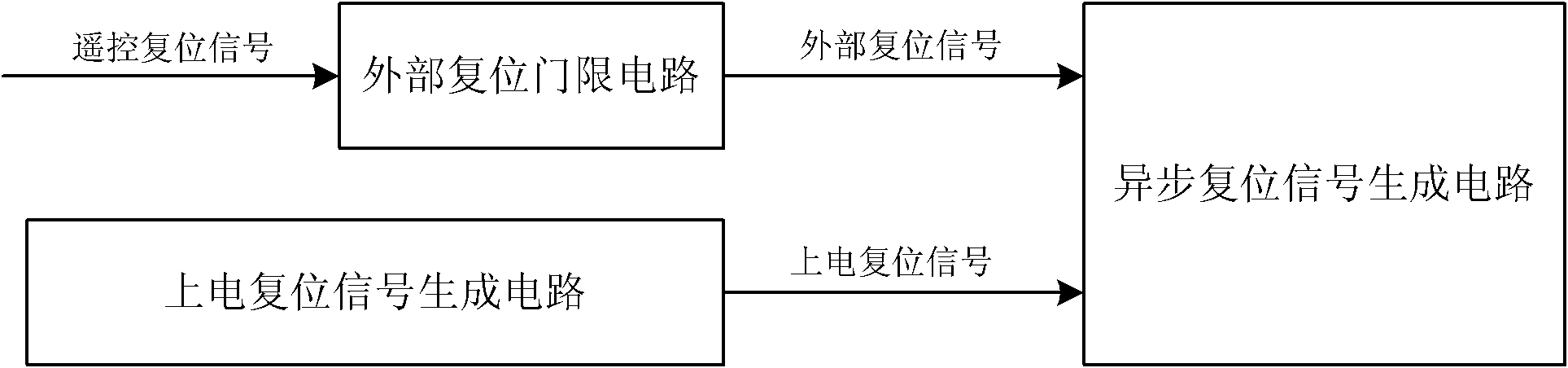

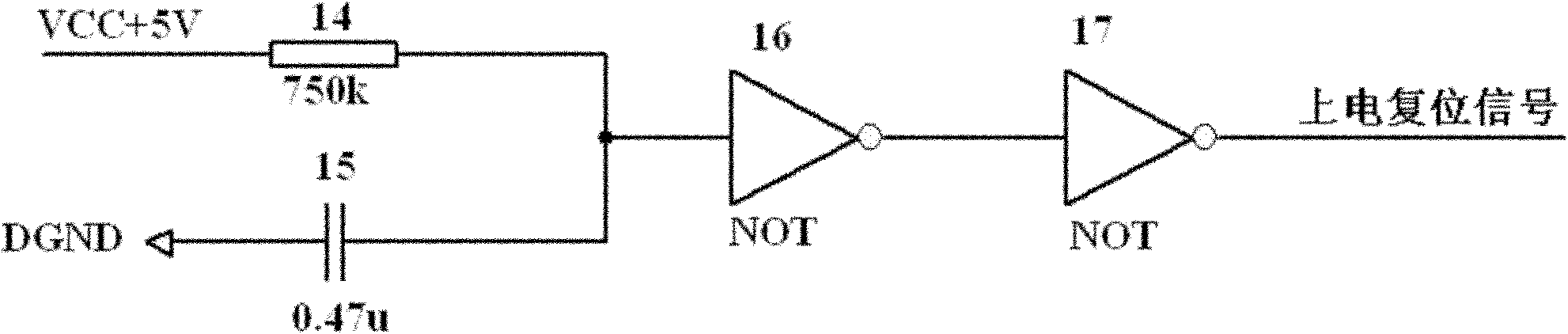

[0029] Such as figure 1 As shown, an anti-fuse type FPGA system reset circuit includes an external reset threshold circuit, a power-on reset signal generation circuit and an asynchronous reset signal generation circuit.

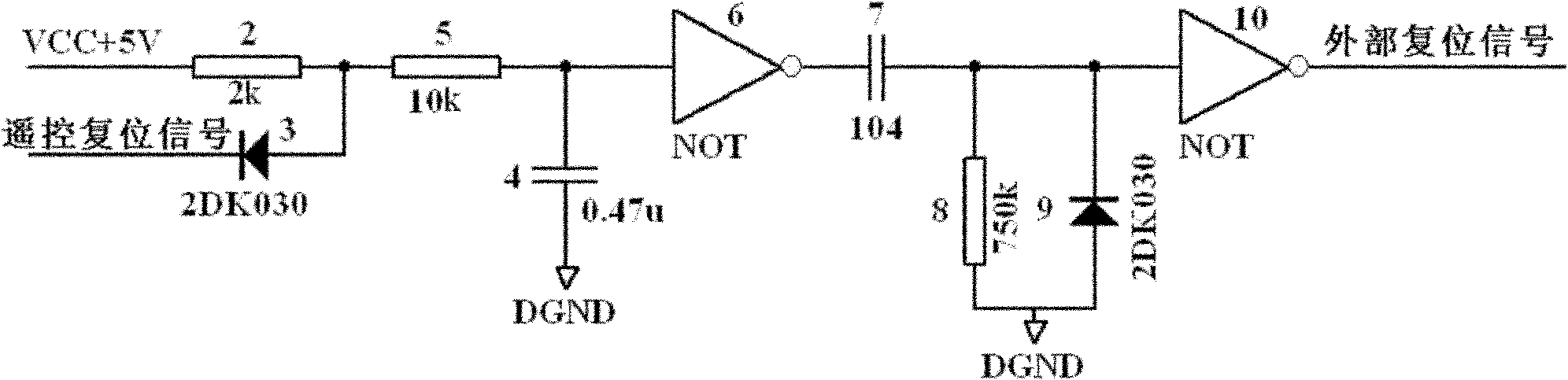

[0030] The external reset threshold circuit is connected with the asynchronous reset signal generating circuit, which receives the remote reset signal, removes the jitter in the remote reset signal, and provides an external reset signal for the asynchronous reset signal generating circuit. The external reset signal is an active-low pulse signal, the amplitude of the external reset signal is 3.3V or 5V, and the pulse width is greater than 10ms.

[0031] In this embodiment, for the antifuse type FPGAA42MX36, the amplitude of the asynchronous reset signal is 5V, and the pulse width is 10ms. The externa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com