Packaging structure for ball grid array and manufacturing method for same

A packaging structure and ball grid array technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve problems such as long time consumption, limited chip size, and complicated procedures, and achieve improved Efficiency, prevention of warpage, and reduction of cantilever effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Hereinafter, a ball grid array package structure and a manufacturing method thereof according to embodiments of the present invention will be described in detail with reference to the accompanying drawings. However, the present invention can be implemented in many different ways and should not be construed as being limited to the following examples. In the drawings, the dimensions are exaggerated for clarity, and the same reference numerals are used in different drawings to designate the same components.

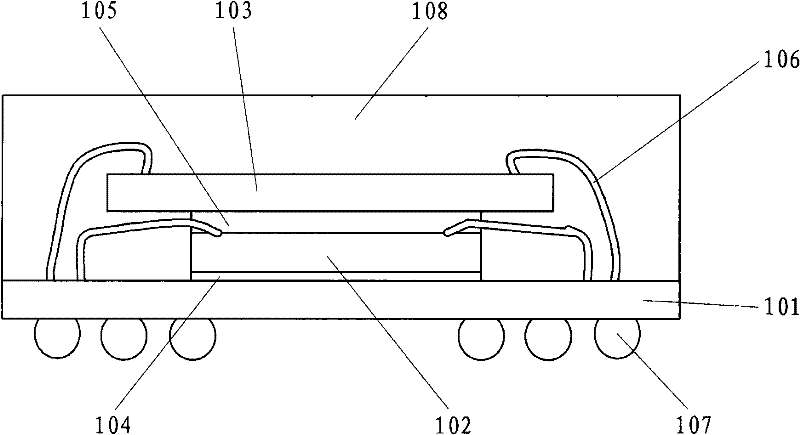

[0025] figure 2 It is a schematic diagram of a multi-chip packaging structure according to an embodiment of the present invention; image 3 It is a flowchart of a manufacturing process of the multi-chip packaging structure according to the present invention; Figure 4 It is a flowchart of another manufacturing process of the multi-chip package structure according to the present invention.

[0026] As can be seen from the figure, the multi-chip ball grid array pack...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com