Sampling clock synchronization method based on decimation/compensation mechanism in ofdm system

A sampling clock synchronization and compensation mechanism technology, applied in synchronization devices, multi-frequency code systems, baseband system components, etc., can solve the problems of system performance degradation, high cost, high noise jitter, etc. Reduce deflection, overcome the effects of high cost and high noise jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The specific implementation of the present invention will be further described below in conjunction with the accompanying drawings, but the implementation and protection scope of the present invention are not limited thereto.

[0049] A sampling clock synchronization method based on decimation / compensation mechanism in OFDM system.

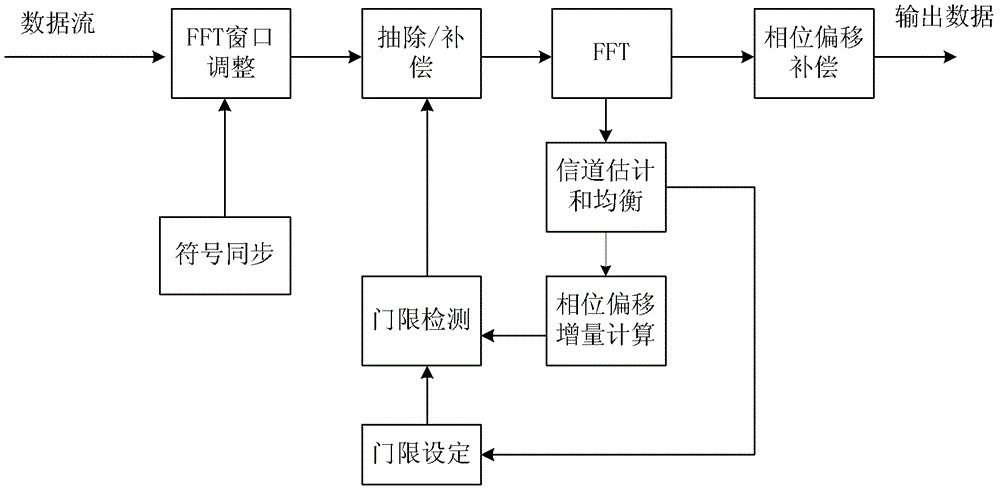

[0050] figure 1 It is a schematic diagram of the sampling clock synchronization method of the OFDM system. It can be seen from the figure that after receiving the data stream, the receiving end first adjusts the FFT window through the symbol synchronization module to find the starting point of the FFT window. Then, through the FFT module, phase offset calculation and threshold detection are performed to determine whether to call the decimation / compensation mechanism. Finally, offset phase angle compensation is performed to complete the clock synchronization process.

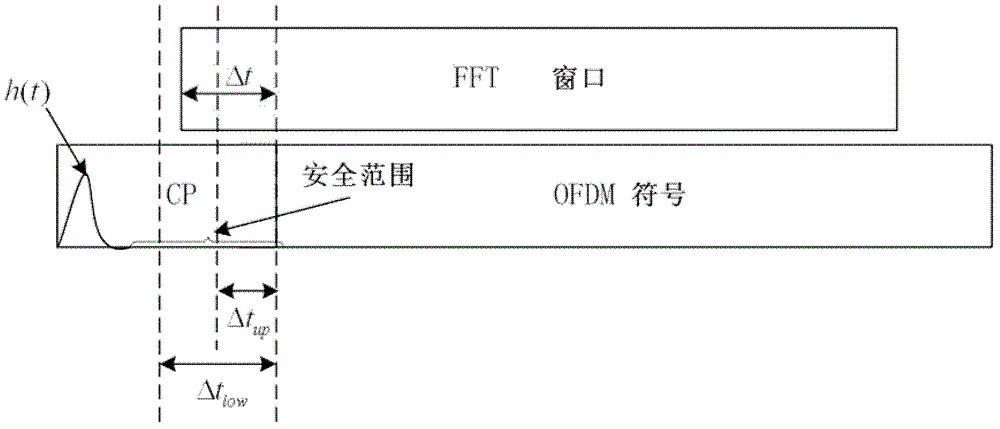

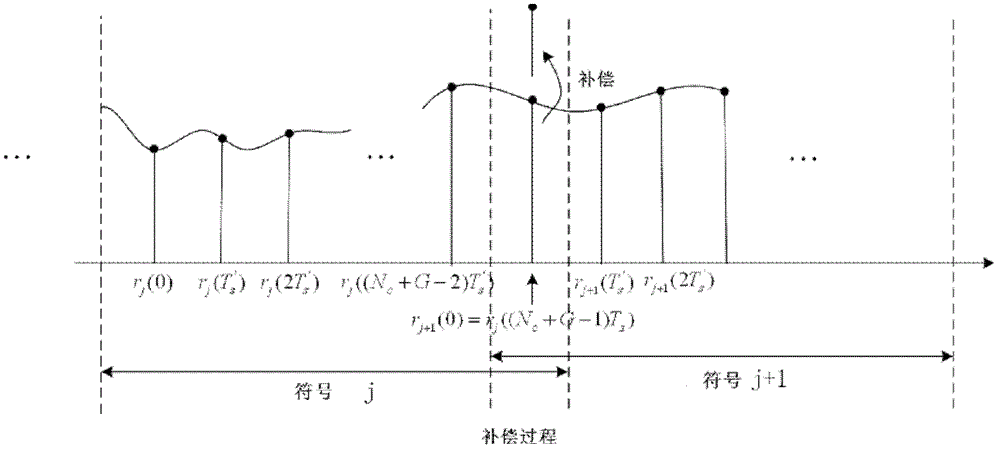

[0051] In order to quantify the sampling frequency deviation between t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com