FPGA (Field Programmable Gate Array)-based lane line detection method

A lane line detection and vanishing point technology, applied in the field of lane line detection, can solve the problems of not being able to meet such huge storage space requirements, low operating frequency and stability, increased cost and area, etc., to save storage devices and save computing time, the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

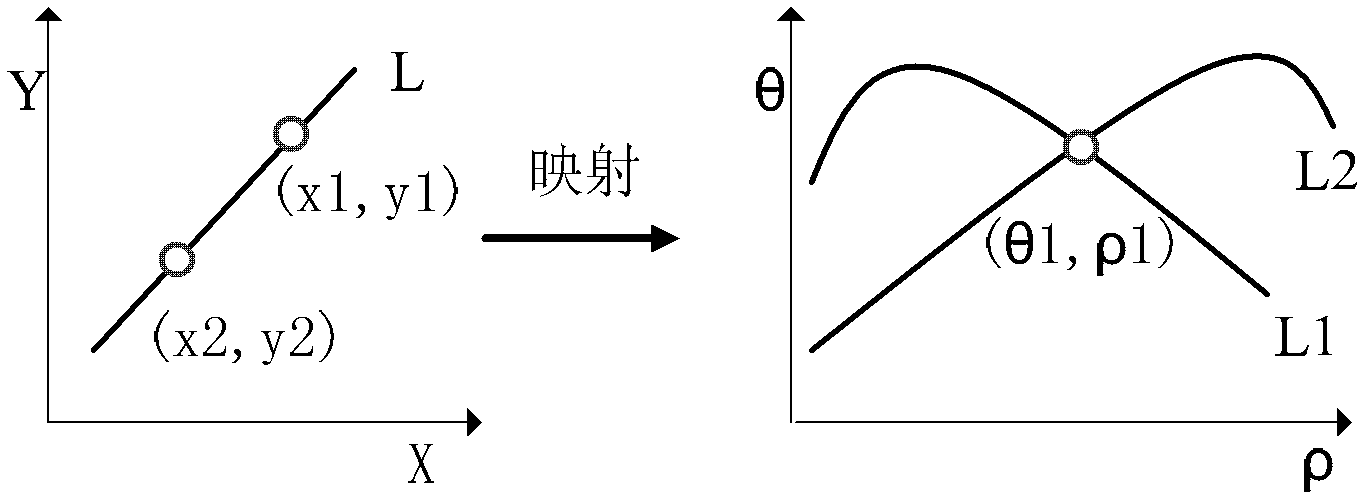

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

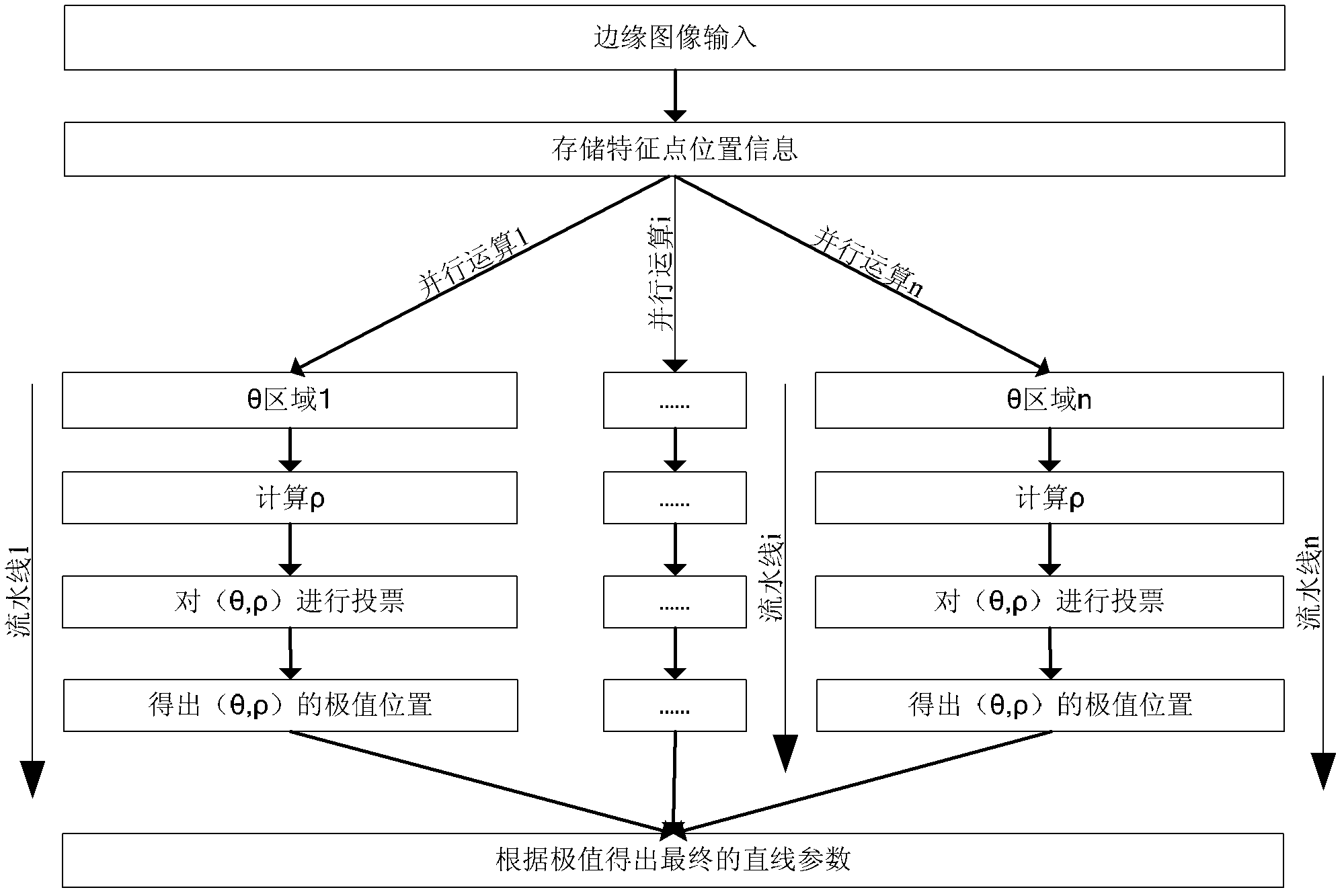

[0039] Such as Figure 7 with Figure 9 Shown, the step of the lane line detection method based on FPGA of the present invention is:

[0040] Step 1: Set the initial parameters, the initial parameters include the initial vanishing point position (x 0 ,y 0 ), parallelism n, constraint range P;

[0041] Step 2: During the driving process of the vehicle, collect the original image I of the road condition in front of the vehicle in real time i , the original image I i is the original image of frame i;

[0042] Step 3: To the original image I i Perform image preprocessing, including median filtering and edge binarization, to obtain the edge image I i edge ;

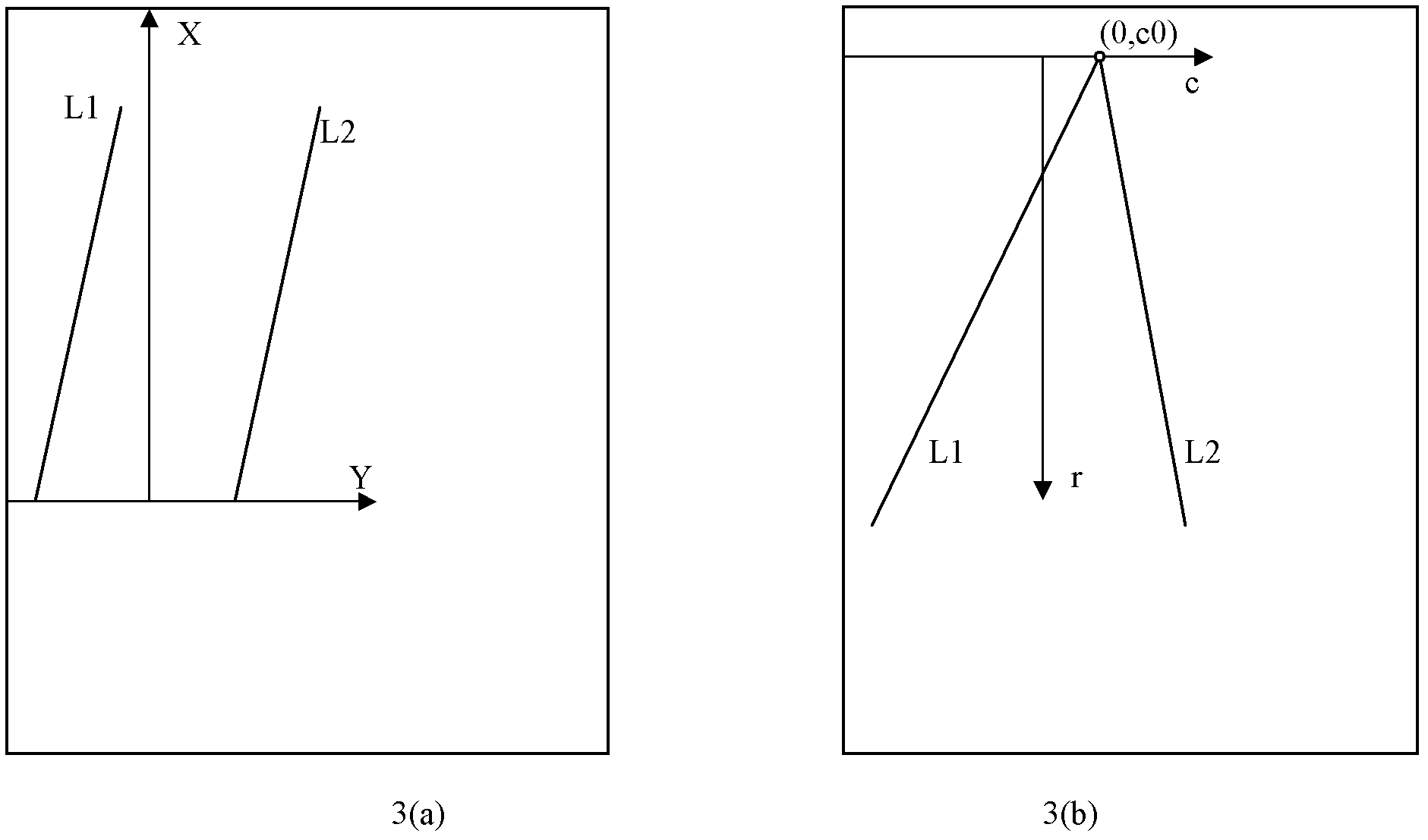

[0043] Step 4: To Edge Image I i edge Coordinate translation: the position of the vanishing point of the previous frame image is known (x i-1 ,y i-1 ), the coordinate sy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com