Partial SOI (silicon on insulator) traverse double-diffused device

A lateral double diffusion, device technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the limitations of limitations, self-heating effects limit development, and surface electric fields are not optimized.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

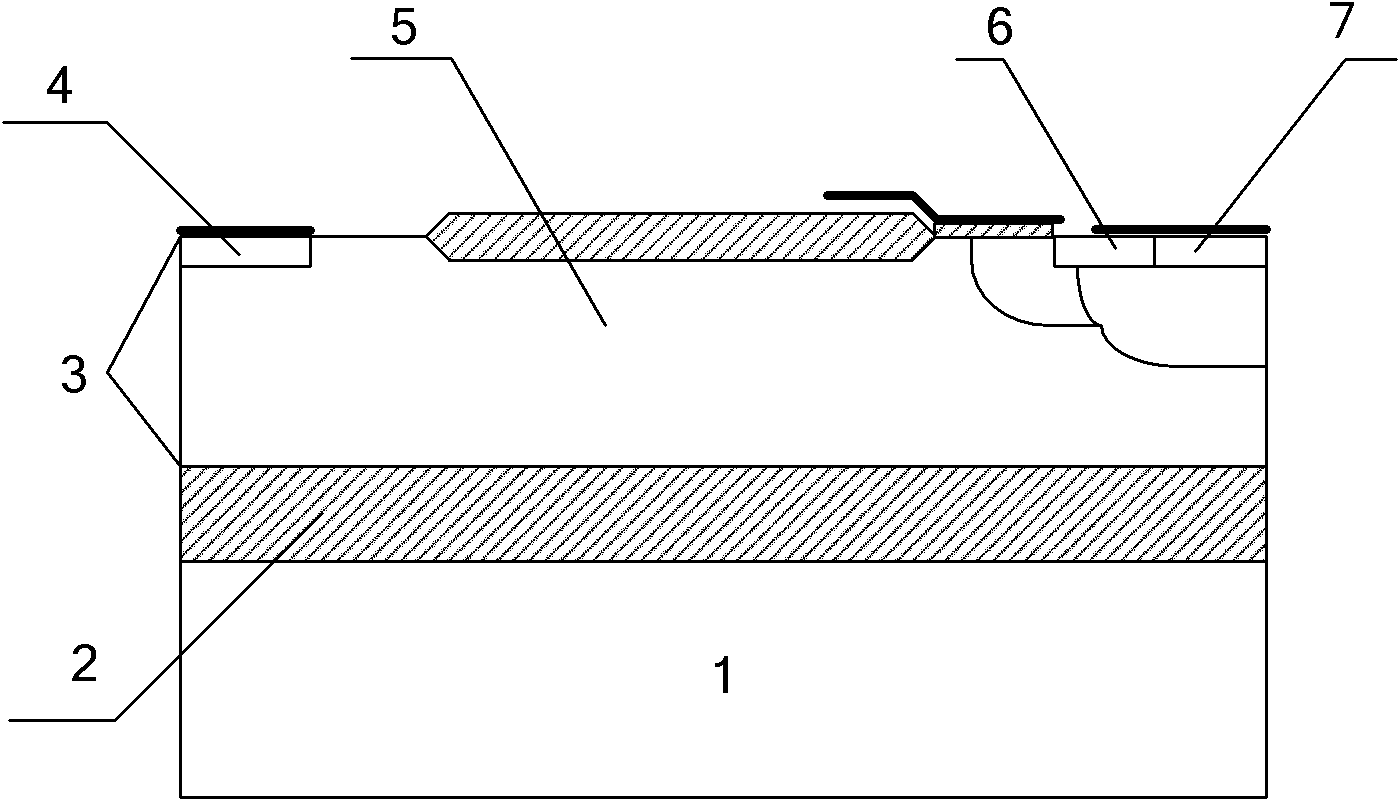

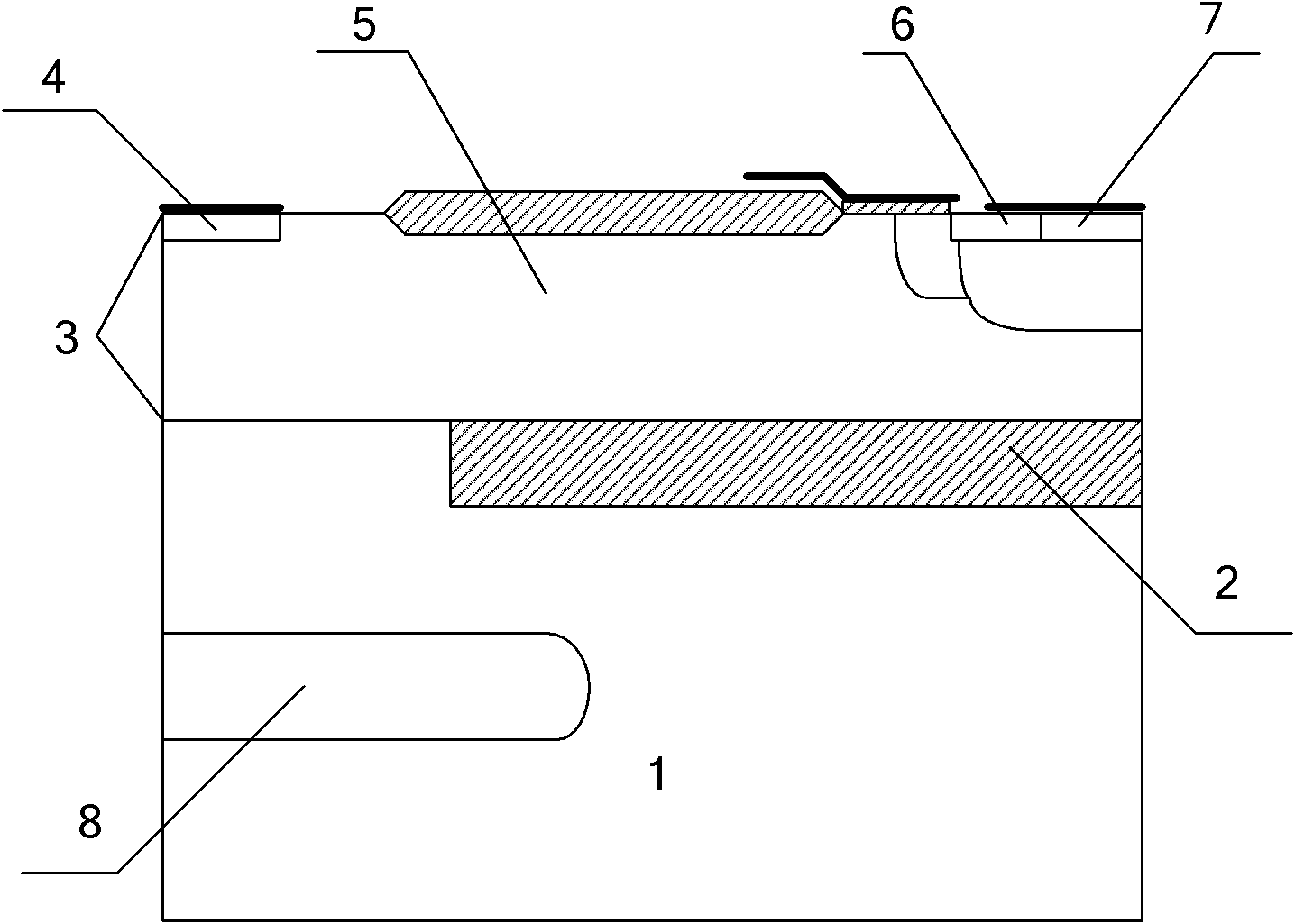

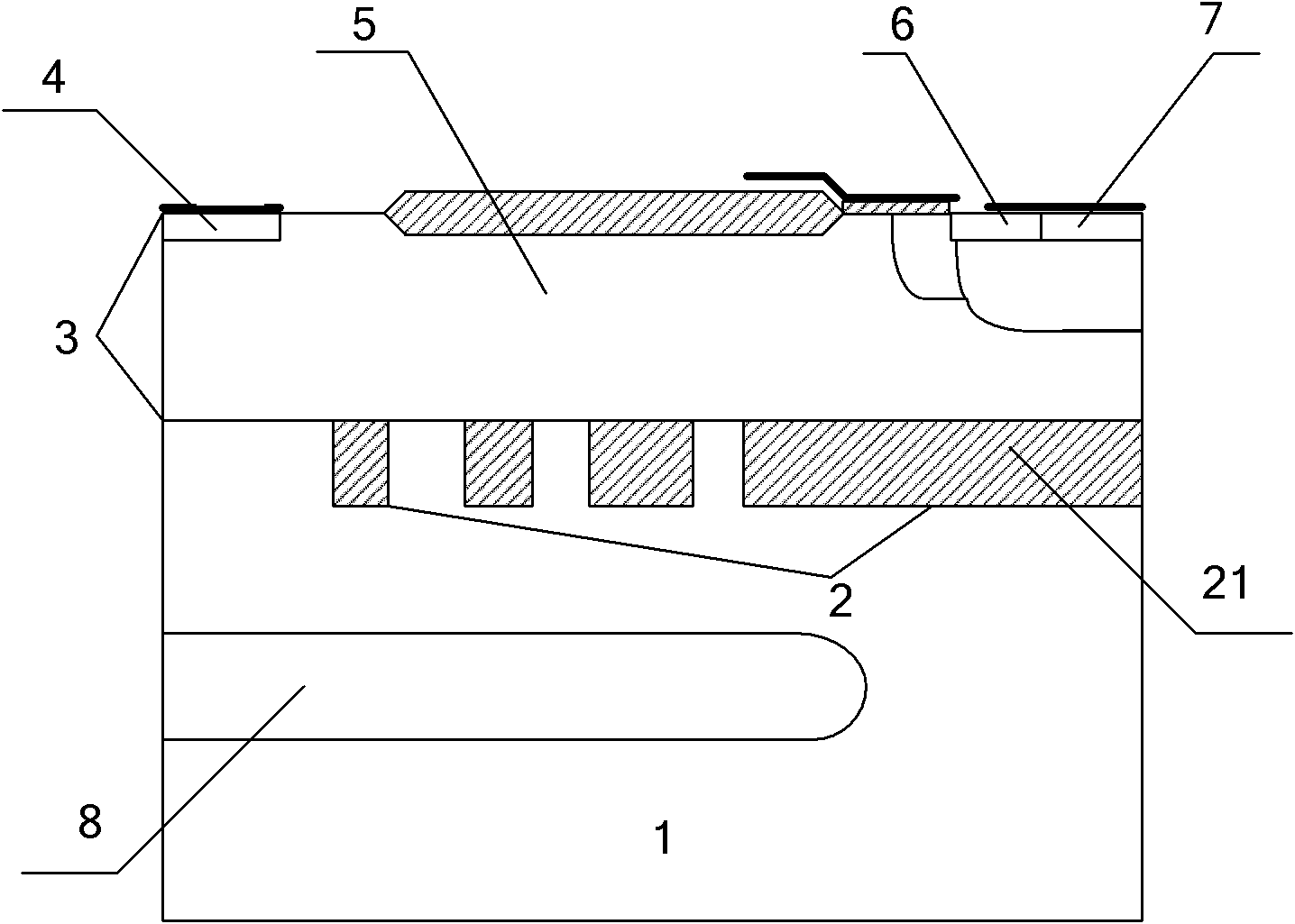

[0024] The buried oxide layer 2 of the partial SOI lateral double-diffusion device in this example can be a continuous layer or discontinuously divided into n segments, and the cross-sectional view when the buried oxide layer is continuous is as follows figure 2 , the cross-sectional view when the buried oxide layer is divided into n segments from one end of the source to the end near the drain is as follows image 3 , the distribution of equipotential lines when a conventional SOI device breaks down is shown in Figure 4 , the distribution diagram of equipotential lines during the breakdown of some SOI lateral double-diffusion devices in this embodiment is as follows Figure 5 , the lateral surface field distribution characteristic curves when the conventional SOI device and the partial SOI lateral double-diffused device of this embodiment break down are as follows Figure 6 , the vertical electric field distribution characteristic curves of the conventional SOI device and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com